### 60V LED Driver with 4A Switch Current

### FEATURES

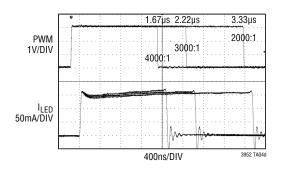

- 4000:1 True Color PWM<sup>™</sup> Dimming

- 4A, 60V Internal DMOS Switch

- Wide Input Voltage Range: 3V to 42V

- OV to 60V Output Current Regulation with Monitor

- PMOS Switch Driver for PWM and Output Disconnect

- LED Short-Circuit Protection and SHORTLED Flag

- Internal Spread Spectrum Frequency Modulation

- Constant-Current and Constant-Voltage Regulation

- Input Current Limit and Monitor

- Adjustable Frequency: 200kHz to 3MHz, Synchronizable to an External Clock

- 10:1 Analog Dimming

- Programmable Open-LED Protection with OPENLED Flag

- Programmable V<sub>IN</sub> Undervoltage and Overvoltage Lockout

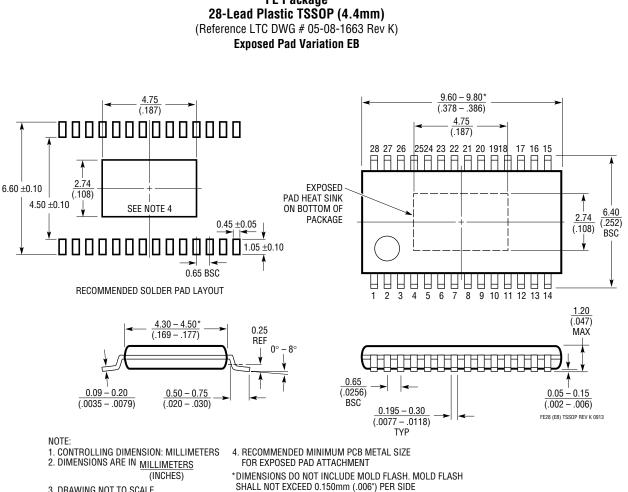

- Available in a 28-Lead TSSOP Package

### **APPLICATIONS**

- Display Backlighting

- Automotive and Avionic Lighting

- Accurate Current-Limited Voltage Regulators

### DESCRIPTION

The LT®3952 is a current mode step-up DC/DC converter with an internal, 60V,  $80m\Omega$  DMOS power switch. The LT3952 is specifically designed to drive high power LEDs in multiple configurations. It combines input and output current regulation loops with output voltage regulation to operate as a flexible current/voltage source.

Programmable switching frequency with optional spreadspectrum modulation provides EMI reduction, while still allowing optimization of the external components for efficiency or component size. The LED current is programmable with an external sense resistor, and can be adjusted from zero to full scale with a voltage at the CTRL pin. The external PWM input provides LED ON/OFF control and 4000:1 dimming ratio, and an internal PWM generator delivers the efficiency of PWM dimming to standalone or I/O limited applications. The LT3952 is available in the thermally enhanced 28-lead TSSOP package.

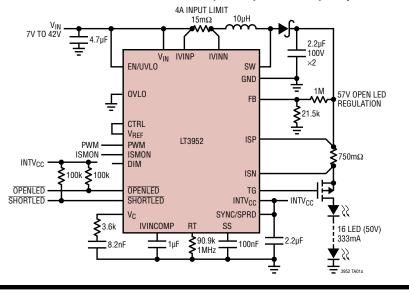

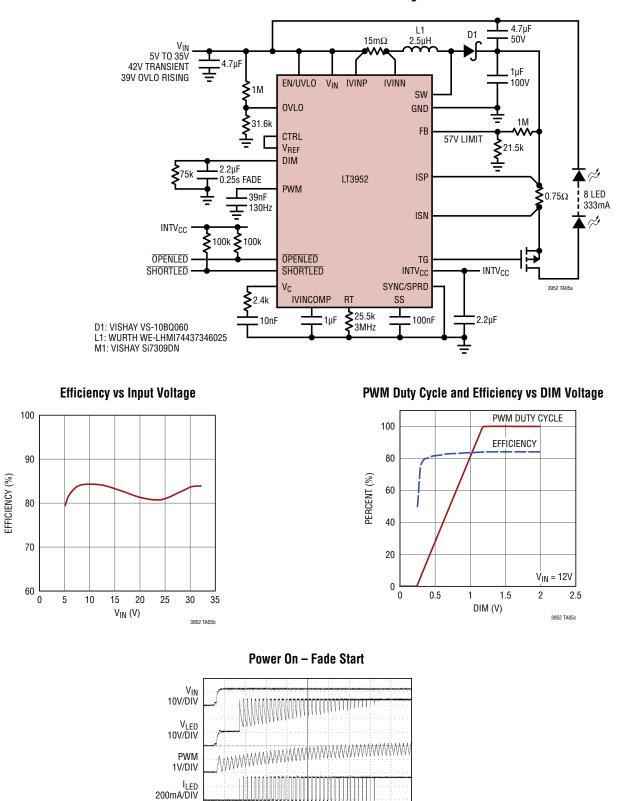

### TYPICAL APPLICATION

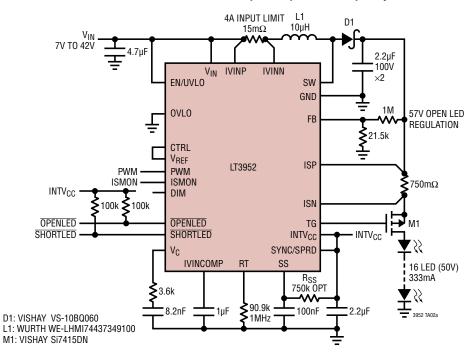

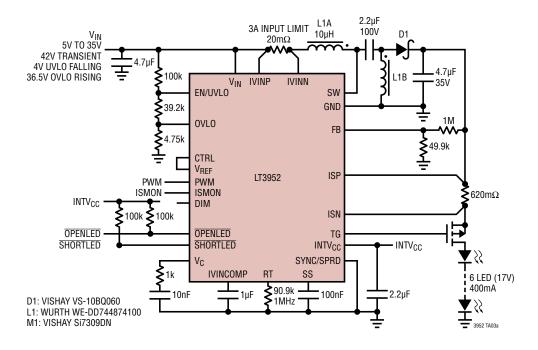

Short-Circuit Robust Boost LED Driver with Spread Spectrum Frequency Modulation

####

VIN (V)

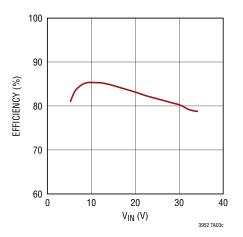

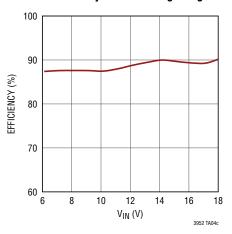

EFFICIENCY (%)

**Efficiency vs Input Voltage**

**LINEAR** TECHNOLOGY 3952fb

3952 TA01E

# ABSOLUTE MAXIMUM RATINGS

| (Note 1)                                                |

|---------------------------------------------------------|

| V <sub>IN</sub> , IVINP, IVINN, SHORTLED, OPENLED,      |

| EN/UVLO                                                 |

| 0VL0                                                    |

| SW, ISP, ISN, TG60V                                     |

| IVINP-IVINN–1V to 3V                                    |

| CTRL, FB, DIM, SYNC/SPRD, PWM INTV <sub>CC</sub> + 0.3V |

| VC, SS, ISMON, IVINCOMP3V                               |

| RT, V <sub>REF</sub> 2V                                 |

| INTV <sub>CC</sub> (Note 4)                             |

| Operating Junction Temperature Range (Notes 2, 3)       |

| LT3952E/LT3952I40°C to 125°C                            |

| LT3952H40°C to 150°C                                    |

| Storage Temperature Range65°C to 150°C                  |

| Lead Temperature (Soldering, 10 sec)                    |

|                                                         |

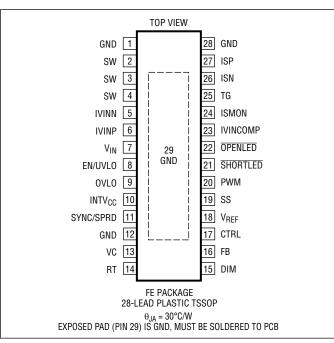

# PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|-----------------|---------------|-----------------------|-------------------|

| LT3952EFE#PBF    | LT3952EFE#TRPBF | LT3952FE      | 28-Lead Plastic TSSOP | -40°C to 125°C    |

| LT3952IFE#PBF    | LT3952IFE#TRPBF | LT3952FE      | 28-Lead Plastic TSSOP | -40°C to 125°C    |

| LT3952HFE#PBF    | LT3952HFE#TRPBF | LT3952FE      | 28-Lead Plastic TSSOP | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = IVINP = IVINN = 12V, ISP = ISN = 24V, EN/UVLO = PWM = 3V, CTRL = 2V, OVLO = OV unless otherwise noted

| PARAMETER                                                                               | CONDITIONS                                                                                                                                           |   | MIN   | ТҮР            | MAX            | UNITS          |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|----------------|----------------|----------------|

| Minimum Operating Voltage                                                               |                                                                                                                                                      |   |       |                | 3              | V              |

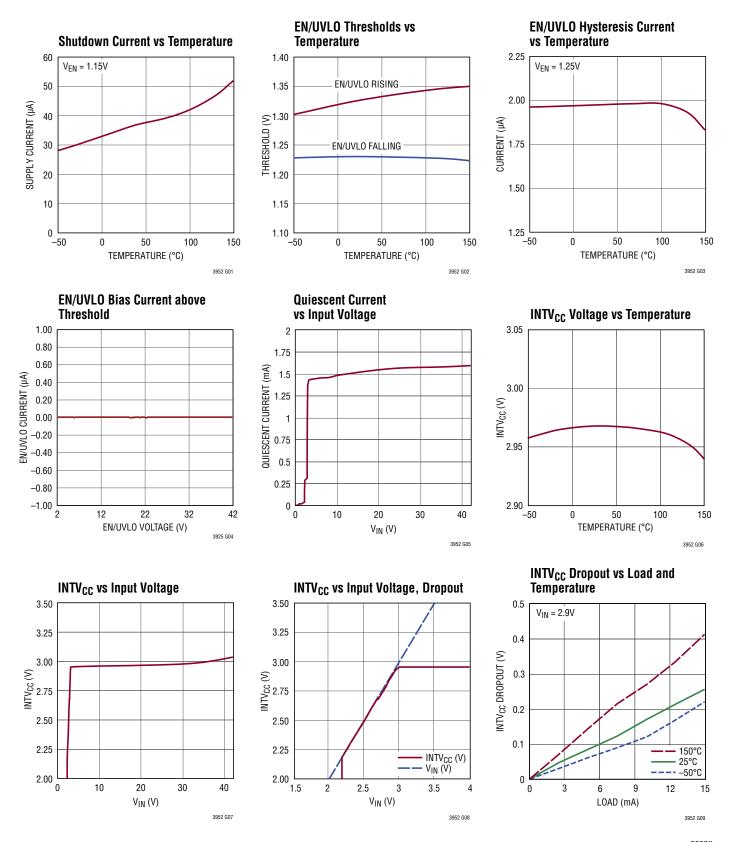

| Supply Current                                                                          | $\label{eq:FB} \begin{array}{l} FB = 1.3 V,  R_{T} = 40.2 k,  CTRL = 0 V \\ EN/UVLO = 0 V,  CTRL = 0 V \\ EN/UVLO = 1.15 V,  CTRL = 0 V \end{array}$ |   |       | 1.5<br>0<br>35 | 2.2<br>1<br>60 | mA<br>μA<br>μA |

| Internal Regulator                                                                      | ·                                                                                                                                                    |   |       |                |                |                |

| INTV <sub>CC</sub> Output Voltage                                                       | CTRL = 0V                                                                                                                                            |   | 2.90  | 3.00           | 3.10           | V              |

| INTV <sub>CC</sub> Dropout Voltage                                                      | $V_{IN} = 3V, CTRL = 0V$                                                                                                                             |   |       | 150            |                | mV             |

| INTV <sub>CC</sub> Undervoltage Lockout                                                 | INTV <sub>CC</sub> Rising, CTRL = 0V                                                                                                                 |   | 2.62  | 2.68           | 2.74           | V              |

| INTV <sub>CC</sub> UVLO Hysteresis                                                      | CTRL = 0V                                                                                                                                            |   |       | 200            |                | mV             |

| Reference Voltage Output                                                                |                                                                                                                                                      |   |       |                | · · · ·        |                |

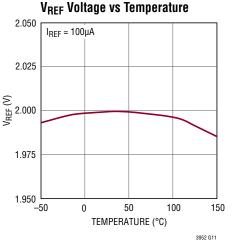

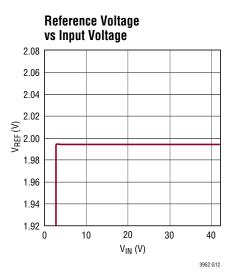

| V <sub>REF</sub> Voltage                                                                | $I_{VREF} = -100\mu A$ , CTRL = 0V                                                                                                                   |   | 1.955 | 2.000          | 2.045          | V              |

| V <sub>REF</sub> Line Regulation                                                        | $3V < V_{IN} < 42V$ , CTRL = 0V                                                                                                                      |   |       | 0.01           |                | %/V            |

| V <sub>REF</sub> Load Regulation                                                        | $0\mu A < I_{VREF} < -100\mu A$ , $CTRL = 0V$                                                                                                        |   |       | 0.6            |                | %              |

| Current Feedback                                                                        |                                                                                                                                                      |   |       |                | ·              |                |

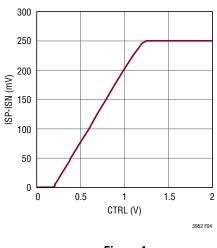

| CTRL Range for Current Sense Threshold Adjustment                                       |                                                                                                                                                      |   | 0.2   |                | 1.2            | V              |

| CTRL PWM Shutdown Threshold                                                             | CTRL Falling                                                                                                                                         |   |       | 100            | 125            | mV             |

| CTRL PWM Threshold Hysteresis                                                           |                                                                                                                                                      |   |       | 12.5           |                | mV             |

| CTRL Zero-Scale Offset                                                                  |                                                                                                                                                      |   |       | 200            |                | mV             |

| CTRL Input Bias Current                                                                 | CTRL = 0V, Current Out of Pin                                                                                                                        |   |       | 20             | 100            | nA             |

| Current Sense Common Mode Input Range                                                   | CTRL = 1.5V                                                                                                                                          |   | 0     |                | 60             | V              |

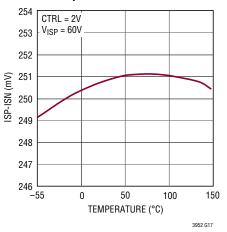

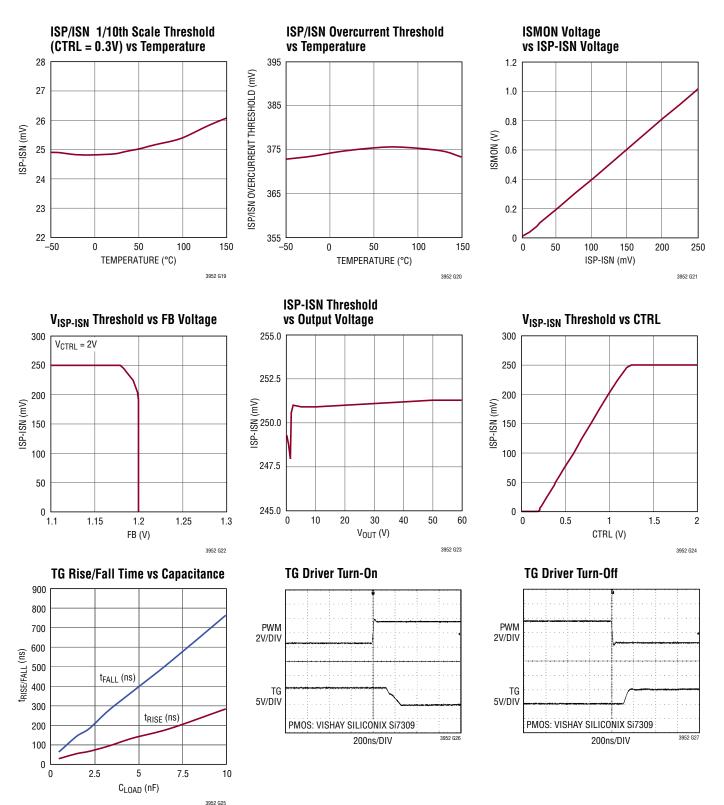

| Full-Scale Current Sense Accuracy (V <sub>ISP</sub> -V <sub>ISN</sub> )                 | ISP = 60V, CTRL = 1.5V                                                                                                                               | • | 245   | 250            | 255            | mV             |

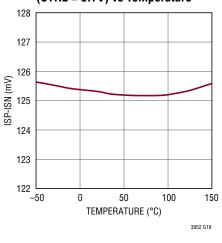

| Midrange Current Sense Accuracy (V <sub>ISP</sub> -V <sub>ISN</sub> )                   | ISP = 60V, CTRL = 0.7V                                                                                                                               |   | 115   | 125            | 135            | mV             |

| 1/10th Scale Current Sense Accuracy (V <sub>ISP</sub> -V <sub>ISN</sub> )               | ISP = 60V, CTRL = 0.3V                                                                                                                               |   | 10    | 25             | 40             | mV             |

| Low Side Current Sense Accuracy (V <sub>ISP</sub> -V <sub>ISN</sub> )                   | ISP = 0V, CTRL = 1.5V                                                                                                                                |   | 240   | 250            | 260            | mV             |

| Overcurrent Sense Threshold                                                             |                                                                                                                                                      |   | 350   | 375            | 390            | mV             |

| ISP to VC Transconductance                                                              | CTRL = 1.5V                                                                                                                                          |   |       | 275            |                | μS             |

| ISP/ISN Input Bias Current                                                              | PWM = 5V (Active), ISP = 60V<br>PWM = 0V (Standby), ISP = 60V                                                                                        |   |       | 250<br>0       | 0.1            | μΑ<br>μΑ       |

| Current Sense Monitor Ratio (V <sub>ISMON</sub> )/(V <sub>ISP</sub> -V <sub>ISN</sub> ) | CTRL = 0.4V, 0.8V                                                                                                                                    |   |       | 4              |                | V/V            |

| Current Sense Monitor Accuracy (V <sub>ISMON</sub> )                                    | CTRL = 1.5V , ISP = 60V                                                                                                                              |   | 0.950 | 1.000          | 1.050          | V              |

| Input Current Sense Amplifier                                                           | ·                                                                                                                                                    |   |       |                | ·              |                |

| Amplifier Supply Current (From IVINP)                                                   | IVINP = IVINN = 42V                                                                                                                                  |   |       | 35             | 60             | μA             |

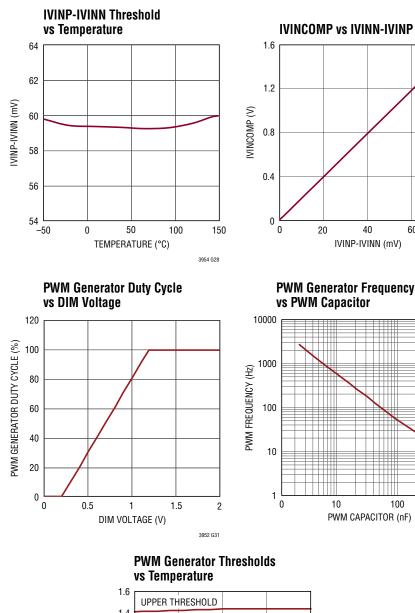

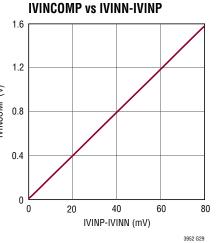

| I <sub>VIN</sub> Regulation Threshold (V <sub>IVINP-IVINN</sub> )                       |                                                                                                                                                      | • | 55    | 60             | 65             | mV             |

| I <sub>VINCOMP</sub> to VC Transconductance                                             |                                                                                                                                                      |   |       | 1650           |                | μS             |

| Input Common Mode Minimum Voltage                                                       |                                                                                                                                                      |   |       |                | 3              | V              |

| IVINP/IVINN to Monitor Voltage Gain                                                     | V <sub>IVINP-IVINN</sub> = 30mV                                                                                                                      |   |       | 20             |                | V/V            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = IVINP = IVINN = 12V, ISP = ISN = 24V, EN/UVLO = PWM = 3V, CTRL = 2V, OVLO = OV unless otherwise noted

| PARAMETER                                                        | CONDITIONS                                                                                                                                       |   | MIN                         | ТҮР                        | MAX                         | UNITS                    |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------|----------------------------|-----------------------------|--------------------------|

| TG Gate Driver                                                   | L                                                                                                                                                | l |                             |                            | ,                           |                          |

| PWM Input High Threshold                                         | PWM Rising                                                                                                                                       |   | 1.15                        | 1.2                        | 1.25                        | V                        |

| PWM Hysteresis                                                   |                                                                                                                                                  |   |                             | 20                         |                             | mV                       |

| TG On Voltage                                                    | V <sub>ISP-TG</sub> , V <sub>ISP</sub> > 10V                                                                                                     |   |                             | 7.5                        | 9.5                         | V                        |

| TG Off Voltage                                                   | V <sub>ISP-TG</sub> , PWM = 0V                                                                                                                   |   |                             | 0                          | 0.3                         | V                        |

| TG Turn-On Time                                                  | C <sub>LOAD</sub> = 470pF, PWM Rising                                                                                                            |   |                             | 100                        |                             | ns                       |

| TG Turn-Off Time                                                 | C <sub>LOAD</sub> = 470pF, PWM Falling                                                                                                           |   |                             | 150                        |                             | ns                       |

| Output Voltage Feedback                                          |                                                                                                                                                  |   |                             |                            |                             |                          |

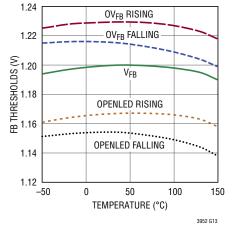

| FB Voltage Regulation Threshold ( $V_{FB}$ )                     | CTRL = 1.5V                                                                                                                                      | • | 1.188<br>1.182              | 1.200<br>1.200             | 1.212<br>1.218              | V<br>V                   |

| FB Open-LED Threshold                                            | FB Rising                                                                                                                                        |   | V <sub>FB</sub> –<br>65mV   | V <sub>FB</sub> –<br>45mV  | V <sub>FB</sub> –<br>25mV   | V                        |

| FB Open-LED Threshold Hysteresis                                 |                                                                                                                                                  |   |                             | 15                         |                             | mV                       |

| FB Overvoltage Threshold                                         | FB Rising                                                                                                                                        |   | V <sub>FB</sub> +<br>15mV   | V <sub>FB</sub> +<br>30mV  | V <sub>FB</sub> +<br>40mV   | V                        |

| FB Overvoltage Threshold Hysteresis                              |                                                                                                                                                  |   |                             | 15                         |                             | m۷                       |

| FB Pin Bias Current                                              |                                                                                                                                                  |   |                             | 20                         | 100                         | nA                       |

| Feedback Line Regulation                                         | 3V < V <sub>IN</sub> < 42V                                                                                                                       |   |                             | 0.0003                     |                             | %/V                      |

| FB to VC Transconductance                                        |                                                                                                                                                  |   |                             | 450                        |                             | μS                       |

| VC Output Impedance                                              |                                                                                                                                                  |   |                             | 5000                       |                             | kΩ                       |

| Soft-Start                                                       |                                                                                                                                                  |   |                             |                            |                             |                          |

| Soft-Start Sourcing Current                                      | Current Out of Pin, SS = 0.1V                                                                                                                    |   | 18                          | 25                         | 37                          | μA                       |

| Soft-Start Sinking Current                                       | SS = 1.8V                                                                                                                                        |   | 1.5                         | 2.5                        | 4.1                         | μA                       |

| Soft-Start Hiccup Retry Threshold                                |                                                                                                                                                  |   |                             | 200                        |                             | mV                       |

| Soft-Start Strong Pull-Down On-Resistance                        |                                                                                                                                                  |   |                             | 120                        |                             | Ω                        |

| Oscillator                                                       |                                                                                                                                                  |   |                             |                            |                             |                          |

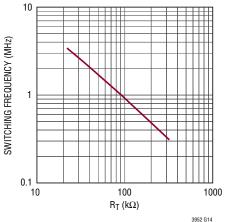

| RT Voltage                                                       |                                                                                                                                                  |   |                             | 1.20                       |                             | V                        |

| Switching Frequency                                              |                                                                                                                                                  | • | 180<br>0.95<br>1.90<br>2.75 | 215<br>1.0<br>2.0<br>3.0   | 250<br>1.05<br>2.10<br>3.25 | kHz<br>MHz<br>MHz<br>MHz |

| Maximum Duty Cycle                                               | $\begin{array}{l} R_{T} = 470k \\ SYNC = 300kHz \ Clock \ Signal, \ R_{T} = 470k \\ R_{T} = 90.9k \\ R_{T} = 40.2k \\ R_{T} = 25.5k \end{array}$ | • | 98<br>97<br>92<br>85        | 99<br>98<br>95<br>90<br>80 |                             | %<br>%<br>%<br>%         |

| Minimum Off-Time                                                 |                                                                                                                                                  |   |                             | 50                         |                             | ns                       |

| Minimum On-Time                                                  |                                                                                                                                                  |   |                             | 75                         |                             | ns                       |

| SYNC/SPRD Pin Resistance to GND                                  | V <sub>SYNC</sub> = 2V                                                                                                                           |   |                             | 100                        |                             | kΩ                       |

| SYNC/SPRD Input High Threshold                                   |                                                                                                                                                  |   | 1.5                         |                            |                             | V                        |

| SYNC/SPRD Input Low Threshold                                    |                                                                                                                                                  |   |                             |                            | 0.4                         | V                        |

| Spread Spectrum Minimum Step as Percentage of ${\rm f}_{\rm SW}$ |                                                                                                                                                  |   |                             | 1                          |                             | %                        |

| Spread Spectrum Maximum Step as Percentage of $f_{SW}$           |                                                                                                                                                  |   |                             | 31                         |                             | %                        |

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = IVINP = IVINN = 12V, ISP = ISN = 24V, EN/UVLO = PWM = 3V, CTRL = 2V, OVLO = OV unless otherwise noted

| PARAMETER                                | CONDITIONS                                                                 |   | MIN                       | ТҮР                       | MAX                        | UNITS       |

|------------------------------------------|----------------------------------------------------------------------------|---|---------------------------|---------------------------|----------------------------|-------------|

| PWM Generator                            | I                                                                          |   |                           |                           | ŀ                          |             |

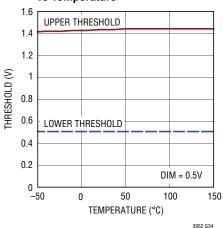

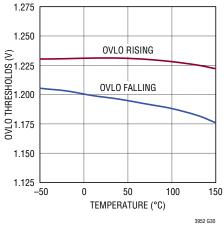

| PWM Pin Pull-Up/Pull-Down Current        | PWM = 1.2V, DIM = 0.7V                                                     | • | 5                         | 10                        | 15                         | μA          |

| PWM Generator Lower Threshold Offset     | 0.2V < DIM < 1.2V                                                          |   | V <sub>DIM</sub> – 15     | V <sub>DIM</sub> + 0      | V <sub>DIM</sub> + 15      | mV          |

| PWM Generator Upper Threshold Offset     | 0.2V < DIM < 1.2V                                                          |   | V <sub>DIM</sub> +<br>825 | V <sub>DIM</sub> +<br>950 | V <sub>DIM</sub> +<br>1075 | mV          |

| PWM Generator Frequency                  | DIM = 0.7V, C <sub>PWM</sub> = 22nF                                        |   |                           | 230                       |                            | Hz          |

| DIM Pin Output Current                   | DIM = 0.7V                                                                 | • | 10                        | 20                        | 30                         | μA          |

| TG Duty Cycle Using PWM Generator        | DIM = 0.345V<br>DIM = 0.535V<br>DIM = 0.725V<br>DIM = 1.105V               |   | 1<br>21<br>42.5<br>86     | 10<br>30<br>50<br>90      | 21<br>39<br>57.5<br>94     | %<br>%<br>% |

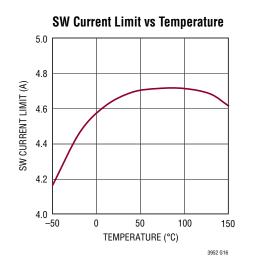

| Power Switch                             |                                                                            |   |                           |                           |                            |             |

| Switch On-Resistance                     | I <sub>SW</sub> = 500mA                                                    |   |                           | 80                        |                            | mΩ          |

| Switch Leakage Current                   | SW = 60V, CTRL = 0V                                                        |   |                           |                           | 2                          | μA          |

| VC to Current Threshold Transconductance |                                                                            |   |                           | 7.5                       |                            | S           |

| Maximum Power Switch Current Limit       | VC = 2V                                                                    |   | 4                         | 4.5                       | 5                          | A           |

| Logic Inputs/Outputs                     |                                                                            |   |                           |                           |                            |             |

| EN/UVLO Disable Threshold                | EN/UVLO Falling                                                            | • | 1.191                     | 1.230                     | 1.269                      | V           |

| EN/UVLO Threshold Internal Hysteresis    |                                                                            |   |                           | 75                        |                            | mV          |

| EN/UVLO Hysteresis Current               | EN/UVLO = 1.25V, Device in Shutdown<br>EN/UVLO = 1.5V, Device in Operation |   |                           | 2<br>0                    | 0.4                        | μΑ<br>μΑ    |

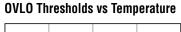

| OVLO Threshold                           | OVLO Rising                                                                | • | 1.191                     | 1.230                     | 1.269                      | V           |

| OVLO Threshold Hysteresis                |                                                                            |   |                           | 25                        |                            | mV          |

| OVLO Input Bias Current                  | 0VL0 = 1V                                                                  |   |                           | 15                        | 100                        | nA          |

| SHORTLED On-Resistance                   | I <sub>SHORTLED</sub> = 1mA                                                |   |                           | 60                        |                            | Ω           |

| SHORTLED Output Low Voltage              | I <sub>SHORTLED</sub> = 2mA                                                |   |                           |                           | 0.3                        | V           |

| SHORTLED Off-State Leakage               | SHORTLED = 42V                                                             |   |                           |                           | 1                          | μA          |

| OPENLED On-Resistance                    | I <sub>OPENLED</sub> = 1mA                                                 |   |                           | 60                        |                            | Ω           |

| OPENLED Output Low Voltage               | I <sub>OPENLED</sub> = 2mA                                                 |   |                           |                           | 0.3                        | V           |

| OPENLED Off-State Leakage                | OPENLED = 42V                                                              |   |                           |                           | 1                          | μA          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT3952E is guaranteed to meet specified performance from 0°C to 125°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT3952I is guaranteed to meet performance specifications over the -40°C to 125°C operating junction temperature range. The LT3952H is guaranteed to meet performance specifications over the  $10^{\circ}$ C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 3:** The LT3952 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed the maximum operating junction temperature when overtemperature is active. Continuous operating above the specified maximum operating junction temperature may impair device reliability. **Note 4:** INTV<sub>CC</sub> is an output and is not meant to be externally driven.

LINEAR

FB Thresholds vs Temperature

Switching Frequency vs  $R_T$

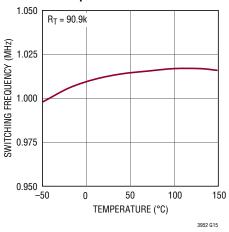

Switching Frequency vs Temperature

ISP/ISN Full-Scale Threshold vs Temperature

ISP/ISN Mid-Scale Threshold (CTRL = 0.7V) vs Temperature

100

1000

3952 G32

**PWM Generator Currents** vs Temperature

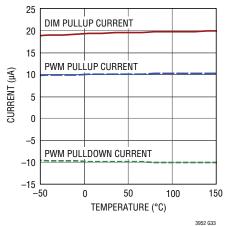

#### **PWM Generator Operation** and Step

### **PIN FUNCTIONS**

GND (1, 12, 28, Exposed Pad Pin 29): Ground Pins. The exposed pad of the LT3952 acts as both GND and heat sink. It must be connected to a large copper area for proper operation.

SW (Pins 2, 3, 4): Switch Pins. Minimize copper area at these pins to increase efficiency and reduce EMI.

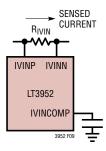

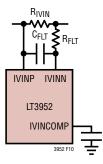

IVINN (Pin 5): Input Current Sense Amplifier Negative Input. The input current sense amplifier reduces the switching current in the case of an overload. VC is reduced when the IVINP-IVINN voltage exceeds the 60mV built-in potential. Tie IVINP-IVINN across an external sense resistor to set auxiliary current limit. If unused, tie to V<sub>IN</sub>.

**IVINP (Pin 6):** Auxiliary Current Sense Amplifier Positive Input. Also acts as the bias supply for the amplifier to provide a function independent from the V<sub>IN</sub> pin. The IVINP/IVINN amplifier can operate from voltages either above or below V<sub>IN</sub>. Tie this pin to the positive terminal of a sense resistor, and do not use resistance in series with this pin. If unused, tie to V<sub>IN</sub>.

V<sub>IN</sub> (Pin 7): Input Supply Pin. Bypass this pin with a capacitor to GND as close to the IC as possible.

**EN/UVLO (Pin 8):** Master Enable and V<sub>IN</sub> Undervoltage Lockout. When low, the IC is put into shutdown mode and the Q current is reduced to <1µA. This pin utilizes a 1.23V comparator with hysteresis, as well as a hysteresis current source for programming additional hysteresis externally. Drive with a digital signal greater than 1.5V for simple on/off control. Tie to a resistor divider between  $V_{\text{IN}}$  and GND to set an external UVLO threshold.

OVLO (Pin 9): Overvoltage Lock Out Comparator. This pin disables switching and TG in the case of an overvoltage. This pin utilizes a 1.23V comparator with hysteresis. When the voltage at OVLO exceeds the threshold, the switching is disabled until the voltage at OVLO falls 25mV below the threshold. Tie to GND if unused.

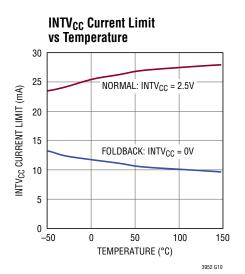

**INTV<sub>CC</sub> (Pin 10):** Internal Low Dropout Regulator Output.  $INTV_{CC}$  is regulated to 3V, and must be bypassed with an external capacitor of at least 2.2µF. INTV<sub>CC</sub> is the power supply for the internal DMOS gate driver and control circuitry. Users may apply <5mA loads to INTV<sub>CC</sub>. Overloading INTV<sub>CC</sub> can cause unintentional device shutdown from  $INTV_{CC}$  falling below the 2.68V UVLO threshold.

SYNC/SPRD (Pin 11): Frequency Synchronization and Spread Spectrum Enable Pin. Tie low for fixed internal clock, tie to INTV<sub>CC</sub> for spread spectrum internal clock, or drive with an external clock for frequency synchronization with no spread spectrum. When using an external clock for frequency synchronization, R<sub>T</sub> resistor should be chosen to program a switching frequency 20% lower than the SYNC pulse frequency. Synchronization (switch turn-on) occurs 50ns after the rising edge of SYNC.

VC (Pin 13): g<sub>m</sub> Amplifier Output for External Loop Compensation. Stabilize the loop with a C or series RC network. This pin is set to a high impedance state during PWM dimming off-time.

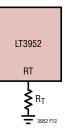

RT (Pin 14): Switching Frequency Adjustment Pin. Set switching frequency using a resistor to GND (see Typical Performance Characteristics for values). For SYNC function, set the frequency 20% slower than the SYNC pulse frequency. Do not leave this pin open. PCB layout must have this component close to the IC.

DIM (Pin 15): PWM Generator Control Voltage. This pin outputs a fixed 20µA current, and controls a triangle wave generator on the PWM pin to determine the PWM duty cycle. 0.2V to 1.2V range on DIM adjusts PWM duty from 0% to 100%. Float this pin or tie to  $INTV_{CC}$  if unused, tie a resistor from DIM to GND to set a fixed voltage, or apply an external voltage to DIM for adjustable PWM duty cycle.

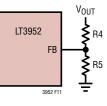

FB (Pin 16): Output Voltage Loop Feedback Pin. Connect to a resistor divider from  $V_{OUT}$ . In constant-voltage applications, FB sets the output voltage. In constant-current applications, the FB divider is set higher than the expected output voltage to act as open-LED protection. As the voltage at FB rises to within 45mV of the regulation point, the **OPENLED** flag is asserted if the output current also falls below one-tenth the full-scale value. If the FB voltage exceeds the regulation point by 30mV, the switching is terminated and the TG pin pulls high in order to disconnect the LED load.

### PIN FUNCTIONS

**CTRL (Pin 17):** Output Current Sense Adjust Pin. Sets voltage regulation threshold across ISP/ISN current sense resistor. 0.2V to 1.2V range on CTRL adjusts ISP/ISN threshold from 0mV to 250mV. Tie to  $V_{REF}$  or INTV<sub>CC</sub> for fixed 250mV threshold. Below 100mV, the CTRL pin acts as an auxiliary PWM input for combination PWM/analog dimming on a single pin.

$V_{REF}$  (Pin 18): Reference Voltage Output. This pin outputs a fixed 2V reference, and supplies up to 100µA for use in generating a reference voltage for the CTRL pin. When using a resistor divider, bypass this pin with 100nF to GND.

**SS (Pin 19):** Soft-Start and Hiccup Control Pin. This pin modulates oscillator frequency and VC voltage clamp when it is below 1.7V. A capacitor on the pin sets the soft-start interval as well as hiccup retry timing in fault mode. The SS pin has a  $25\mu$ A pull-up current in normal mode, a  $2.5\mu$ A pull-down current in hiccup mode, and a  $120\Omega$  pull-down resistance in start-up mode. Optional latchoff mode is set with a 750k pull-up resistor from INTV<sub>CC</sub> to SS.

**PWM (Pin 20):** On/Off Control. Used for TG on/off control and PWM dimming of the LED. Logic low idles regulator to a lower Q current, makes the TG pin drive to  $I_{SP}$  level, and makes the VC pin high impedance. Logic high turns on error amplifier, enables switching and TG. The PWM threshold is 1.2V. Tie to  $V_{REF}$  or  $INTV_{CC}$  for continuous operation. The PWM pin also supplies ±10µA switched current sources to generate a triangle wave on external capacitor for the PWM dimming generator. It is safe to overdrive these currents with an external signal.

**SHORTLED** (Pin 21): Open-Drain Short-Circuit Indicator. SHORTLED pulls low in the case of an LED overcurrent fault, and releases during the start-up phase of the next soft-start cycle. The state of SHORTLED is only updated when the PWM pin is high. Tie this pin to desired logic high voltage with an external resistor. The maximum recommended sink current is 2mA to limit excess power dissipation. Leave the pin open if unused. **OPENLED** (Pin 22): Open-Drain Open-LED Indicator. OPENLED pulls low when the voltage at the FB pin is within 45mV of the regulation point and the LED current has dropped to 10% of the full-scale output. OPENLED releases when the FB voltage falls below the threshold. The state of OPENLED is only updated when the PWM pin is high. Tie this pin to desired logic high voltage with an external resistor. The maximum recommended sink current is 2mA to limit excess power dissipation. Leave the pin open if unused.

**IVINCOMP (Pin 23):** Auxiliary Current Sense Amplifier Monitor Output. The voltage at IVINCOMP is a  $20 \times$  amplified and buffered version of the IVINP-IVINN differential voltage, and the VC voltage will be reduced when IVIN-COMP reaches its 1.2V threshold. A 1µF capacitor to GND is suggested to filter inductor ripple and compensate the input current loop. During PWM dimming, the IVINCOMP pin stores the input current regulation loop value on the capacitor during the PWM off time. Do not load this pin. If the input current regulation loop is not used, this pin may be connected to GND.

**ISMON (Pin 24):** Output Current Monitor Pin. The voltage at ISMON is a  $4 \times$  amplified and buffered version of the ISP, ISN differential voltage. During PWM dimming, the ISMON voltage continues to reflect the instantaneous output current, falling during the PWM low time.

**TG (Pin 25):** Top Gate Driver Output. An inverted and levelshifted version of the PWM input signal. Drives the gate of an external PMOS transistor between  $V_{ISP}$  and  $V_{ISP}$ -7.5V to provide load-side on/off control, PWM dimming, and fault mode disconnect. Leave TG unconnected if not used.

**ISN (Pin 26):** Output Current Sense Amplifier Negative Input. Connect this pin to the load side of the output current sense resistor. If unused, tie to output voltage.

**ISP (Pin 27):** Output Current Sense Amplifier Positive Input. Also serves as the positive rail for the TG driver. Limit impedance in series with this pin.If unused, tie to output voltage.

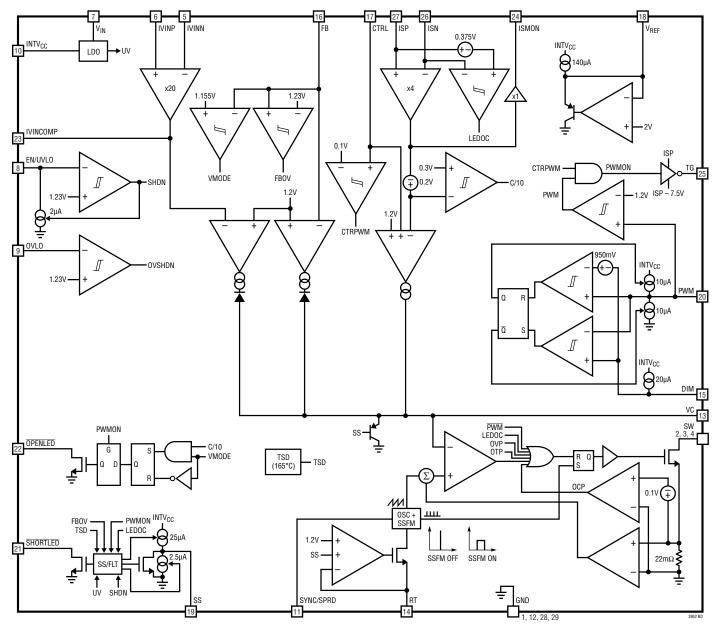

# **BLOCK DIAGRAM**

The LT3952 is a fixed-frequency, current mode boost converter with a feature set ideal for driving high power LED lamps. It provides input and output current regulation, as well as output voltage regulation and fault handling. The operation of the LT3952 is best understood by referring to the Block Diagram. In normal operation, with the PWM pin low, the switching is disabled, the TG pin is pulled high to ISP to turn off the PMOS disconnect switch, the VC pin is high impedance to store the previous switching state on the external compensation capacitor, and the ISP/ISN pin bias currents are reduced to leakage levels.

When the PWM pin transitions high, the TG pin transitions low after a short delay. At the same time, the internal oscillator wakes up and generates a pulse to set the PWM latch, turning on the internal NMOS power switch. The switch current is sensed and added to a stabilizing slope compensation ramp, and the resultant signal is compared to the VC voltage. The inductor current increases linearly during the switch on-time. When the current sense signal exceeds the VC value, the latch is reset and the internal NMOS power switch is turned off. During the switch off-time, energy is transferred from the inductor and the inductor current decreases. At the completion of each oscillator cycle, internal signals such as slope compensation return to their starting points and a new cycle begins with the set pulse from the oscillator.

Through this repetitive action, the IC establishes a switching duty cycle to regulate a current or voltage in the load. The VC signal is integrated over many switching cycles, and is an amplified version of the difference between the LED current sense voltage, measured between ISP and ISN, and the target difference voltage set by the CTRL pin. In this manner, the error amplifier sets the correct peak switch current level to keep the LED current in regulation. If the error amplifier output increases, more current is demanded in the switch; if it decreases, less current is demanded. If the switch current exceeds the internal 4.5A current limit, the latch is reset regardless of the state of the PWM comparator. Likewise, in any fault condition; i.e., FB overvoltage (V<sub>FB</sub> > 1.23V), LED overcurrent (V<sub>ISP-ISN</sub> > 375mV), overvoltage lockout or INTV<sub>CC</sub> undervoltage the switching is immediately disabled.

In addition to the V<sub>ISP-ISN</sub> to CTRL feedback loop, the LT3952 also provides additional loops to control input current and output voltage. The loops are connected in a wired-OR configuration, where the auxiliary loops are only allowed to reduce the value of VC in the event that one or more exceeds its threshold. This means that even if one or more of the auxiliary loops is below its regulation point, VC will not rise unless the output (LED) current sense is also below its regulation point.

The first auxiliary loop is the output voltage feedback loop using the FB pin. It is typically used to prevent the output voltage from exceeding a safe value. The voltage at the FB pin is compared to an internal reference voltage of 1.2V, and the amplified difference pulls down the VC pin in the case that FB exceeds 1.2V. As VC drops, the switching current reduces and in this manner the output voltage is regulated so that FB = 1.2V.

The second auxiliary loop is the input current limit using the IVINN, IVINP, and IVINCOMP pins. Similar to the output (LED) current loop, the input current is sensed as the differential voltage across a sense resistor. As the average IVINP/IVINN differential voltage exceeds 60mV, IVINCOMP reaches its 1.2V threshold, and VC is reduced in order to limit the input current to the 60mV threshold.

### INTV<sub>CC</sub> Bypass Capacitor

$INTV_{CC}$  is the internal power supply for the IC, and supplies the gate drive to the internal power switch. A bypass capacitor is required from  $INTV_{CC}$  to GND for stability and filtering of the switching noise. For best results, use a ceramic capacitor of  $2.2\mu F$  or greater, and place the capacitor as close to the IC as possible.

### V<sub>REF</sub> Bypass Capacitor

$V_{\text{REF}}$  is the 2V reference output and can be bypassed with 100nF to GND. For best results, place the bypass capacitor close to the IC and away from the noisy switching nodes.

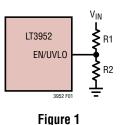

# Programming the Turn-On/Turn-Off Thresholds with the EN/UVLO Pin

The LT3952 provides an adjustable V<sub>IN</sub> undervoltage lockout (UVLO) function using the EN/UVLO pin. The EN/UVLO function provides a precision 1.23V falling threshold with 75mV internal hysteresis as well as a 2µA pull-down current in the off state to provide additional, user-programmable hysteresis. This pin can also be driven with a logic level greater than 1.5V or tied to V<sub>IN</sub> for always-on operation. In order to program an external UVLO, tie the EN/UVLO pin to a resistor divider between  $V_{IN}$  and GND. The divider ratio determines the baseline turn-off/turn-on thresholds and the value of the upper resistor determines the additional hysteresis.

The most important (and precise) threshold is the turnoff threshold from  $V_{\text{IN}}$  falling. The following equations determine the resistor values:

$$V_{UV(FALLING)} = 1.23 \cdot \left(1 + \frac{R1}{R2}\right)$$

$$V_{UV(RISING)} = 1.305 \cdot \left(1 + \frac{R1}{R2}\right) + 2\mu A \cdot R1$$

For example, a 12V falling UVLO with roughly 10% total hysteresis requires 185k for R1. The closest standard value is 187k, therefore:

# **OPERATION** Programming the Overvoltage Disable with the OVLO Pin

It is also possible to program a disable threshold if the input voltage rises too high. The OVLO pin has a 1.23V comparator with 25mV internal hysteresis. If the voltage at OVLO exceeds the 1.23V threshold, the switching is disabled, TG pulls high, and the SS pin pulls low. The device begins a new soft-start sequence when the voltage at OVLO has fallen 25mV below the threshold.

Although it is possible to connect this pin with an independent resistor divider, the component count is minimized by splitting the bottom resistance of the standard EN/UVLO divider to generate an additional tap point.

Using the previous values of R1 and R2 from the UVLO section, the new R3 value is computed using the desired rising threshold by:

$$R3 = 1.23 \cdot \left(\frac{R1 + R2}{V_{OV(RISING)}}\right)$$

The middle resistor will be designated R2A. To obtain the value for R2A, subtract the calculated value of R3 from the old R2 value.

Continuing the previous equation, the desired value of R3 is 8k for an OVLO threshold of 32V. Subtract this from the previous value of R2 in order to find the value of R2A. In our case, R3 = 8.06k and the closest 1% resistor for the new R2A value is 13.3k. The thresholds are recalculated if desired from the expanded divider ratios:

$$V_{UV(FALLING)} = 1.23 \cdot \left(1 + \frac{R1}{R2A + R3}\right)$$

$$V_{UV(RISING)} = 1.305 \cdot \left(1 + \frac{R1}{R2A + R3}\right) + 2\mu A \cdot R1$$

$$V_{OV(RISING)} = 1.23 \cdot \left(1 + \frac{R1 + R2A}{R3}\right)$$

$$V_{OV(FALLING)} = 1.205 \cdot \left(1 + \frac{R1 + R2A}{R3}\right)$$

In our example:

$\label{eq:relation} \begin{array}{l} R1 = 187 \text{k}, \ R2\text{A} = 13.3 \text{k}, \ R3 = 8.06 \text{k} \\ \\ V_{\text{UV}(\text{FALLING})} = 11.998 \text{V} \\ \\ V_{\text{UV}(\text{RISING})} = 13.104 \text{V} \\ \\ V_{\text{OV}(\text{RISING})} = 31.796 \text{V} \\ \\ V_{\text{OV}(\text{FALLING})} = 31.151 \text{V} \end{array}$

3952f

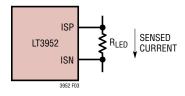

### LED Current Control and Monitor

The LED current is programmed through the combination of an external sense resistor and a voltage on the CTRL pin. The CTRL voltage adjusts the setpoint of the current sense amplifier on the ISP and ISN pins from 0mV to 250mV, and the external sense resistor defines the output current for a given setpoint. The current sense resistor is typically placed at the top of the LED strand, although the rail-to-rail ISP/ISN inputs allow placement at the bottom of the strand as well.

Figure 3

The required sense resistor for a desired output current is computed by:

$$R_{LED} = \frac{V_{ISP-ISN}}{I_{OUT}}$$

In the case of the fixed 250mV setpoint:

$$R_{LED} = \frac{0.25}{I_{OUT}}$$

For example, a 500mA output requires a  $0.5\Omega$  sense resistor when using the fixed 250mV setpoint.

In adjustable mode, the working range of CTRL is from 0.2V to 1.2V and adjusts the setpoint of ISP and ISN from 0mV to 250mV. In this manner, analog dimming is achieved.

The required CTRL voltage for a desired analog setpoint is computed by:

$V_{CTRL} = 0.2 + 4 \cdot V_{ISP-ISN}$

As the CTRL voltage nears 1.2V, a crossover from adjustable threshold to a precision internal 250mV setpoint takes place and some nonlinearity occurs as shown in the ISP-ISN vs CTRL graph in the Typical Performance Characteristics. It is therefore desirable to drive the CTRL pin well above 1.2V when the 250mV setpoint is desired. Tying CTRL to the 2V  $V_{\text{REF}}$  output is an excellent method of doing so.

### **LED Current Monitoring**

The ISMON pin provides a buffered output representing the differential voltage on ISP-ISN for current monitoring applications. The normal working range of ISMON is from OV to 1V, and the gain from ISP-ISN to ISMON is 4. This corresponds to a 1V output at ISMON when the ISP-ISN differential voltage has reached the 250mV maximum.

#### External PWM Dimming

The PWM pin, in combination with an external PMOS transistor driven from the TG pin, allows on/off control and PWM dimming of the LED current.

The PWM pin has a fixed 1.2V threshold, and driving PWM higher than 1.2V enables the device for switching and causes the TG pin to drive to a level roughly 7.5V lower than the voltage at ISP. During the low time of PWM, the TG pin is driven to the voltage at ISP to turn off the external PMOS, and the LT3952 is put into a low power standby state. Switching and the error amplifiers are disabled and the VC pin is three-stated to preserve the value of VC voltage for accelerated start-up upon the next rising edge of PWM.

The CTRL pin also offers a PWM function to allow analog and digital dimming on a single pin. Below 0.1V on CTRL, the device is also put into standby mode with SW, TG, and the error amplifiers disabled. Keep in mind that between 0.2V and 0.1V on CTRL, the device is not disabled, although the output current is commanded to 0. The value of VC reduces towards the minimum, and TG keeps the output PMOS enabled, which discharges the output through the LED lamps. For effective PWM dimming using the CTRL pin, please ensure that the low voltage on CTRL is below 0.1V. This is easily obtained using an external open-drain device to pull down a resistor divider used to generate the CTRL setpoint. Alternately, enabling and disabling a DAC output driving CTRL also gives excellent results.

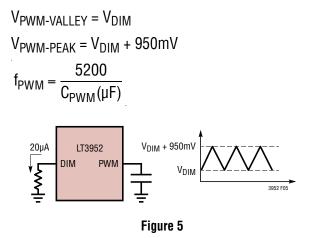

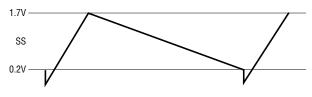

#### **Internal PWM Generator**

The PWM pin can also provide a self-oscillating PWM generator for standalone operation by simply tying a small capacitor from PWM to GND. In this configuration, 10µA

pull-up and pull-down current sources generate a triangle waveform on the PWM pin whose peak and valley points are defined by the voltage on the DIM pin and whose frequency is defined by the external capacitor.

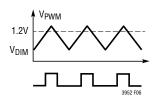

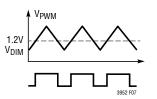

By raising and lowering the voltage on the DIM pin, the triangle wave intersects the 1.2V PWM threshold at different points, changing the PWM duty cycle.

Figure 6. Lower DIM Voltage

Figure 7. Higher DIM Voltage

As the DIM pin exceeds 1.2V, the PWM duty cycle will be 100%. As the DIM pin exceeds 2.3V, the internal PWM generator is disabled along with the switched 10 $\mu$ A pull-down on PWM. The PWM pin will continue to be pulled to INTV<sub>CC</sub> with the 10 $\mu$ A pull-up current. For applications utilizing external PWM dimming, it is recommended to disable the internal PWM generator by floating the DIM pin or tying it to INTV<sub>CC</sub>. This will provide the fastest PWM response for high dimming ratios.

Programming the frequency of PWM dimming consists only of selecting the proper capacitor for the PWM pin according to:

$$C(nF) = \frac{5200}{f_{PWM}(Hz)}$$

A common selection is 39nF for roughly 133Hz.

Programming the PWM duty cycle consists of setting a voltage on the DIM pin according to:

$V_{\text{DIM}(V)} = 0.95 \cdot \text{Duty} + 0.25$

As shown in Figure 5, a single resistor in combination with the  $20\mu A$  output current of DIM can be used to program the duty cycle.

$R_{DIM(k\Omega)} = 47.5 \cdot Duty + 12.5$

For adjustable duty cycle control, an external voltage can be applied at the DIM pin using a DAC or external supply.

To slowly increase the light output upon start-up or restart, a capacitor can also be used with the DIM circuit. To fade from dark to full brightness, only a capacitor is required. To fade from dark to a fixed duty cycle, place a capacitor in parallel with the DIM resistor.

Upon start-up or fault retry, an internal pull-down with 2k series resistance is applied to the DIM pin to discharge any external capacitor before the start-up sequence begins. Be aware that this will temporarily load an external voltage applied to DIM.

Figure 8. Fade on to Full Brightness, or to Preset Duty

3952fh

### Input Current Limit

The LT3952 provides adjustable input current limiting through the IVINP/IVINN/IVINCOMP amplifier. Connect the IVINP and IVINN sensing terminals across a resistor in series with the input. A 20x amplified version of the IVINP–IVINN differential is generated at IVINCOMP. A capacitor at IVINCOMP provides filtering and averaging of the input ripple.

As the average IVINP–IVINN differential reaches 60mV, the IVINCOMP voltage will reach its 1.2V regulation threshold and the cycle-by-cycle switch current will be reduced. In this manner, the input current is regulated to 60mV differential between IVINP and IVINN.

$$R_{SENSE} (m\Omega) = \frac{60mV}{I_{IN(LIM)}(A)}$$

For example, a 2.4A input current limit is programmed with a  $25m\Omega$  sense resistor.

Figure 9

In some cases, such as deep discontinuous conduction, a large input ripple current may cause the input current limit to activate early, cutting into the typical regulation profile. In this situation, it is possible to filter the ripple down to a smoother level using an external RC network.

Be aware that input current on start-up and PWM dimming is larger than steady state due to the output current required to fill the output capacitor. It is recommended to set the input limit appropriately to prevent interruption of the regulated output.

### **Input Current Monitor**

An input current monitor is available as the voltage on IVINCOMP, which reflects a voltage equal to  $20 \times$  the IVINP-IVINN differential voltage and has a working range of 0V to 1.2V as the IVINP-IVINN voltage varies from OmV to 60mV.

IVINCOMP is a high impedance output and should not be loaded. Averaging of current sense ripple, and compensation of the feedback loop is achieved using a  $1\mu$ F capacitor from IVINCOMP to GND.

### **Output Voltage Regulation/Limiting**

The LT3952 provides a voltage-feedback error amplifier through the FB pin to provide output voltage regulation and limiting for open-LED protection.

In the case of an open-LED strand, the current commanded by CTRL is never achieved and the device continues to drive the output voltage higher. If left unchecked, this could result in overvoltage damage to the external components and the power switch itself, and therefore an output voltage limit is required.

By connecting FB to a resistor divider between  $V_{OUT}$  and GND, the maximum output voltage regulates at the 1.2V threshold of the FB pin. The maximum output voltage is computed as follows:

$$V_{OUT} (V) = 1.2 \cdot \left(1 + \frac{R4}{R5}\right)$$

<sup>3952fb</sup>

A simple method to determine the proper resistor values is to choose a value of R5 that draws a tolerable amount of current at the 1.2V regulation point, and to compute R4 by using:

$$R4 = (V_{0UT} - 1.2) \cdot \frac{R5}{1.2}$$

For example, R5 = 24k draws  $50\mu$ A at the regulation point, and for a 24V output limit, the desired value of R4 is 456k. The closest standard value to this is 453k, providing 23.85V output voltage limit.

It is necessary to set the regulation point slightly higher than the worst-case voltage drop of the LEDs to avoid cut-in of the voltage limit during normal regulation.

### Open LED Flag and Overvoltage Protection

The LT3952 provides an indicator of the open-LED condition on the OPENLED pin, as well as an internal overvoltage detection to prevent output overshoot if the LED strand goes open under load. Both of these features are based on the voltage at the FB pin.

The  $\overrightarrow{OPENLED}$  pin consists of an open-drain NMOS pull down to be connected with an external pull-up resistor to the user's desired voltage. This pin tolerates up to 42V, and has a pull-down strength of  $60\Omega$ . Please be aware of power dissipation and keep the  $\overrightarrow{OPENLED}$  current to a few mA maximum. The OPENLED pin pulls low when the following two conditions are met:

- 1. The voltage at FB rises to within 45mV of the 1.2V regulation point.

- 2. The output current is detected to be less than one-tenth of the value commanded by CTRL.

The OPENLED pin releases when the voltage at FB falls to 65mV below the 1.2V regulation point. This sequence prevents false OPENLED flags from momentary overshoot.

An overvoltage condition is detected by the voltage at FB rising to 30mV above the 1.2V regulation point. Upon detection of an overvoltage condition, the switching is disabled and TG is pulled high to disconnect and protect the load. Switching is re-enabled when the FB voltage falls by 15mV. An overvoltage condition does not affect the state of the OPENLED pin.

### **Switching Frequency**

The switching frequency is programmed with a resistor from the RT pin to GND. The RT pin is regulated to 1.2V, and the output current of  $R_T$  adjusts the oscillator frequency.

Figure 12

The overall switching period is defined by the sum of two parts: a fixed 50ns off-time that defines  $D_{MAX}$ , and a variable time defined by the RT current. To determine the proper  $R_T$  value for a desired switching frequency, using the following equation:

$$\mathsf{R}_{\mathsf{T}}(\mathsf{k}\Omega) = \frac{88.9}{\mathsf{f}_{\mathsf{SW}}(\mathsf{MHz})^{1.13}}$$

For example, a 2MHz switching frequency results in a desired  ${\sf R}_{\sf T}$  resistance of 40.6k, which has 40.2k as the closest standard value.

Table 1 provides some commonly used values.

| R <sub>T</sub> (kΩ) |  |  |  |  |

|---------------------|--|--|--|--|

| 25.5                |  |  |  |  |

| 40.2                |  |  |  |  |

| 90.9                |  |  |  |  |

| 243                 |  |  |  |  |

| 470                 |  |  |  |  |

|                     |  |  |  |  |

Table 1. Switching Frequency vs  $R_T$  Value

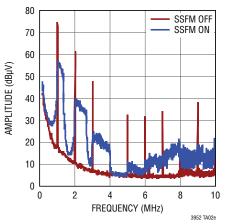

#### Frequency Synchronization and Spread Spectrum

The LT3952 SYNC pin acts as both an external clock input for frequency synchronization and the enable signal for internal spread spectrum feature. Tie the SYNC/SPRD pin low for fixed-frequency internal clock, tie to  $INTV_{CC}$  for spread-spectrum internal clock, or drive with an external clock for frequency synchronization with no internal spread spectrum. When synchronizing to an external clock, the  $R_T$  resistor should be chosen to program a switching frequency 20% lower than the external clock frequency. Even when synchronizing, a soft-start cycle will first start the oscillator in frequency foldback to minimize inrush current. As the soft-start cycle nears completion, the device will then transition to the external frequency.

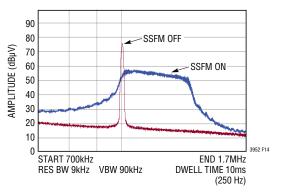

When the SYNC/SPRD pin is tied high for greater than 32 clock cycles, the device will enable spread-spectrum clocking for EMI reduction. By continuously varying the oscillator frequency, spread spectrum distributes the EMI power generated during the switching cycle over a group of frequencies rather than concentrating it at a single frequency. Therefore, the measured EMI power at any single frequency is reduced compared to that of fixedfrequency operation.

In spread-spectrum mode, the oscillator frequency is varied in a pseudorandom manner from the nominal frequency to 31% above nominal in 1% steps. This unidirectional adjustment allows LT3952 to avoid a sensitive band in the system simply by programming the nominal frequency slightly above it. The proportional step size allows the user to easily determine  $R_T$  value for their specified EMI test bin size, and the pseudorandom method provides tone suppression from the frequency variation itself.

The pseudorandom value is updated proportionally to the oscillator frequency, using a rate of  $f_{SW}/32$ . This rate allows multiple passes of the entire group of frequencies during standard EMI test dwell times.

Figure 13. Average Conducted EMI – 1MHz

### Inductor Selection

Inductor selection consists of two parameters: saturation current rating and inductance value. A higher switching frequency allows the use of a smaller inductance value at the expense of increased switching loss.

The saturation current rating of the inductor is selected appropriately for the 4A current limit of the device.

An approximation for maximum inductor current (efficiency = 100%) is based on the maximum LED current and the input/output ratio:

$$I_{L(MAX)}(A) = \left(\frac{V_{LED(MAX)}}{V_{IN(MIN)}}\right) \cdot I_{LED}$$

The maximum steady-state inductor current,  $I_{L(MAX)}$ , should be less than 3A to allow for current ripple and transient response. The desired inductance is determined based on the steady-state current ripple. A typical rule of thumb is to set the inductor current ripple to a maximum of 25% of the switch current limit.

Boost:

$$L_{BOOST} \ge \frac{V_{IN(MIN)} \left( V_{LED(MAX)} - V_{IN(MIN)} \right)}{V_{LED(MAX)} \cdot 1A \cdot f_{SW}}$$

Buck:

$$L_{BUCK} \ge \frac{V_{LED(MAX)} \left( V_{IN(MIN)} - V_{LED(MAX)} \right)}{V_{IN(MIN)} \cdot 1A \cdot f_{SW}}$$

Buck-Boost:

$$L_{BB} \geq \frac{\left(\frac{V_{IN(MIN)} \bullet V_{LED(MAX)}}{V_{LED(MAX)} + V_{IN(MIN)}}\right)}{f_{SW} \bullet 1A}$$

Table 2 provides some recommended inductor vendors.

#### Table 2. Inductor Manufacturers

| VENDOR           | WEB               |

|------------------|-------------------|

| Wurth Elektronik | www.we-online.com |

| Coilcraft        | www.coilcraft.com |

| Cooper           | www.cooperet.com  |

#### **Output Capacitor Selection**

In the case of driving LEDs, their exponential current/ voltage characteristic dictates that output voltage ripple translates almost directly to LED current ripple. Although the effect is not visible to the eye, large LED current ripple may affect the output current accuracy and color spectrum and it is therefore advisable to keep the output voltage ripple below a few percent.

For the boost and buck-boost topologies, output current is delivered in pulses and the filtering requirement is higher than for the buck topology with its continuous output current. Assuming a low ESR ceramic capacitor and 25% inductor current ripple, use the following equations to compute the required output capacitance for a desired output ripple voltage,  $\Delta V_{LED}$ .

Boost, Buck-Boost:

$$C_{OUT} = \frac{I_{LED} \cdot (V_{LED} - V_{IN})}{V_{LED} \cdot \Delta V_{LED} \cdot f_{SW}}$$

Buck:

$$C_{OUT} = \frac{0.3 \cdot I_{LED}}{8 \cdot \Delta V_{LED} \cdot f_{SW}}$$

### **Input Capacitor Selection**

The input capacitor is also selected based on desired voltage ripple. Complementary to output capacitor selection, the discontinuous input current of the buck topology requires more filtering than the continuous input current of the boost or buck-boost. Use the following equations to determine the input capacitance required for a desired input ripple voltage,  $\Delta V_{IN}$ .

Boost, Buck-Boost:

$$C_{IN} = \frac{O.3 \cdot I_{LED} \cdot \frac{V_{LED}}{V_{IN}}}{8 \cdot \Delta V_{IN} \cdot f_{SW}}$$

Buck:

$$C_{IN} = \frac{V_{IN} \cdot I_{LED} \cdot (V_{IN} - V_{LED})}{\Delta V_{IN} \cdot V_{IN}^2 \cdot f_{SW}}$$

### **Schottky Rectifier Selection**

The power Schottky diode conducts the switching current during the switch off-time. Select a diode rated for at least  $1.5 \cdot I_{LED}$  to account for current variation from efficiency and inductor ripple. The reverse-breakdown voltage should be at least 20% greater than the maximum reverse voltage expected in circuit.

#### **Loop Compensation**

The LT3952 uses an internal transconductance error amplifier whose VC output compensates the control loop. The external inductor, output capacitor and the compensation resistor and capacitor determine the loop stability. The inductor and output capacitor are chosen based on performance, size and cost. The compensation resistor and capacitor at VC are selected to optimize control loop response and stability. For typical LED applications, a 6.8nF to 10nF compensation capacitor at VC is adequate, and a series resistor increases the slew rate on the VC pin to maintain tighter regulation of LED current during fast transients on the input supply of the converter.

### External PMOS Disconnect/PWM Switch

A high side PMOS disconnect switch with a minimum  $V_{TH}$  of –2V is recommended in most LT3952 applications. This switch is enabled and disabled during PWM dimming, and disconnects the output in shutdown and during fault conditions. Select a PMOS transistor with a  $V_{DS}$  rating greater than the open-LED regulation voltage set by FB, and with a continuous current rating greater than I<sub>LED</sub>.

### Soft-Start

The LT3952 incorporates flexible soft-start and the option of hiccup or latchoff mode for customizing fault response. The SS pin provides a 25 $\mu$ A pull-up current for charging, a 2.5 $\mu$ A pull-down current for discharging, and a 120 $\Omega$ NMOS pull-down switch for clearing an external softstart capacitor. The state of each of these components is determined by the soft-start/fault sequence, and will be described herein.

**Shutdown Mode:** During shutdown mode, all SS currents and the pull-down switch are disabled, effectively

three-stating the SS pin. This is to avoid sinking quiescent current in the case that an external resistor pull-up is connected to SS.

When the device leaves shutdown mode, the NMOS pulldown switch is activated to clear the voltage at the soft-start capacitor. The device waits in this state until the voltage at SS drops below 0.2V, and until start-up is enabled as defined by PWM > 1.2V and CTRL > 100mV. If both enable signals are already valid upon leaving shutdown mode, the NMOS pull-down is activated for 10µs longer than is required to pull the SS voltage below 0.2V. In all cases, this action provides a start-up profile where the initial voltage at SS can be considered approximately 0V.

In the event that the device is shut down by EN/UVLO or the INTV<sub>CC</sub> voltage dropping below 2.68V, the SS pin initially goes high impedance and then restarts the clear, charge sequence as described.

**Start-Up Mode:** Once start-up is enabled by PWM and CTRL both valid, the NMOS pull-down switch is disabled and the 25µA charging current is enabled. The voltage at SS begins ramping in a linear manner until it reaches 0.2V, at which point switching and the TG driver are enabled. From 0.2V to 1.7V on SS, the frequency and the current limit are increased linearly with SS voltage to provide a smooth start-up profile with low inrush current. The required soft-start capacitor for a desired start-up time is computed from the 1.5V range of SS and the 25µA charge current.

$C_{SS}$  (nF) = 16.67 •  $t_{SS}$  (ms)

For example, a soft-start time of roughly 0.5ms is generated with an 8.2nF capacitor.

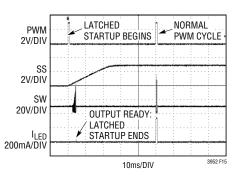

Depending on output and load conditions the device may enter regulation before SS reaches 1.7V, however it is the combination of the 1.7V threshold and the sensing of at least one-tenth of the output current defined by CTRL that signifies the successful completion of soft-start. This becomes important when start-up is enabled by a low duty cycle PWM signal. The explanation is as follows:

A low duty cycle PWM signal could cause excessive start-up times if it were allowed to interrupt the softstart sequence. Therefore, once start-up is initiated by PWM > 1.2V and CTRL > 150mV, it temporarily ignores a logical disable by either of those signals. The device continues to soft-start with switching and TG enabled until either the voltage at SS reaches the 1.7V level, or the output current reaches one-tenth of the full-scale value. At this point the device begins following the dimming control as designated by PWM or CTRL. If at any time an output overcurrent is detected, SW and TG will be disabled even as SS continues to charge. This will be discussed in further detail in the Fault Handling section.

#### Figure 14. PWM Latched Startup

One note is when PWM dimming using CTRL, the output current is commanded to zero during the low time of CTRL even as the soft-start voltage rises.

**Fault Handling:** Although the fault handling sequence may change based on the soft-start conditions, the switching is disabled and the TG driver immediately pulls high upon detection of an output overcurrent fault. This provides safe output disconnect even in the case of a dead short on the output.

When an overcurrent is detected and TG and SW are disabled, SS is still required to charge to the 1.7V upper threshold before it begins discharging back down using the 2.5 $\mu$ A current source. If SS is already at or above 1.7V, it begins discharging immediately upon the disable of TG and SW. If SS is still in the start-up phase when an output overcurrent fault is detected, then SS continues charging even as TG and SW are disabled. It charges to the 1.7V level before reversing direction and discharging to the 0.2V level with the 2.5 $\mu$ A current source. This provides additional delay to allow the system to recover from the overcurrent condition.

Once SS has discharged to the 0.2V level, the sequence of clearing SS with the  $120\Omega$  NMOS pull-down and restarting the  $25\mu$ A charge phase reoccurs as previously described. Switching and TG are not re-enabled until SS again climbs to the 0.2V threshold. If at this point an overcurrent is still detected, then SW and TG are again disabled as SS continues to climb to the 1.7V threshold before reversing direction. In this manner, a hiccup retry cycle is obtained with a maximum switching duty cycle of 10%, the ratio of 25µA pull-up to 2.5µA pull-down currents. This low hiccup duty cycle reduces input power during sustained overload conditions.

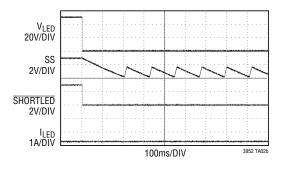

Figure 15. SS in Sustained Hiccup Mode

If a latched-off response is desired, a user simply sets a pull-up resistor from INTV<sub>CC</sub> to SS with a value low enough to prevent SS from discharging to the 0.2V level. For the low pull-down current of 2.5 $\mu$ A, even a relatively large value of 750k to INTV<sub>CC</sub> prevents SS from reaching the automatic retry threshold and effectively provides a fault latchoff. At this point, a manual retry is obtained by entering and exiting shutdown mode, upon which the 120 $\Omega$  NMOS pull-down clears the SS voltage in preparation for retry.

**SHORTLED** Flag: The LT3952 provides an open-drain SHORTLED pin to flag the overcurrent detection. This pin is connected with a pull-up resistor to the user's voltage (up to 42V), and has a pull-down strength of  $60\Omega$ . Please be aware of power dissipation and keep the pull-up current to a few mA maximum.

The SHORTLED pull-down activates immediately upon detection of a fault and stays on throughout the charge/ discharge phase of the hiccup cycle. The pull-down releases

as the SS capacitor is cleared to 0V during the restart phase and stays released as SS re-charges to the 0.2V retry threshold. If at this point a fault is again detected, the pin is again pulled down as the hiccup retry cycle continues. For the user detecting fault with an IRQ, this falling edge is used to count a desired number of faults before full system shutdown, or the rising edge is used to prepare the system for a new start-up cycle.

### **Board Layout**

The high speed operation of the LT3952 demands careful attention to board layout and component placement. The exposed pad of the package is the GND terminal of the IC and is also important for thermal management of the IC. It is crucial to achieve a good electrical and thermal contact between the exposed pad and the ground place of the board. To reduce electromagnetic interference (EMI), it is important to minimize the area of the high dV/ dt switching node between the inductor, SW pins, and anode of the Schottky rectifier.

Use a ground plane under the switching node to eliminate interplane coupling to sensitive signals. The length of the high dl/dt trace from the SW pin through the Schottky rectifier and filter capacitor to GND should be minimized, and the IC GND pins should be connected to the large copper area beneath the IC. The GND terminal of the INTV<sub>CC</sub> capacitor should be placed near the GND of the switching path. The ground for the V<sub>REF</sub> capacitor, the IVINCOMP capacitor, the compensation network, and other DC control signals should be star connected to the underside of the IC. Do not route high impedance signals such as FB, DIM, IVINN, RT and VC near the switching nodes, and minimize the length of their routes to avoid picking up switching noise.

Since there is a small, but variable, DC bias current on the ISP/ISN/IVINP/IVINN inputs, minimize resistance in series with these pins to avoid creating an offset. Kelvin connecting these lines to the terminals of their respective sense resistors provides best performance.

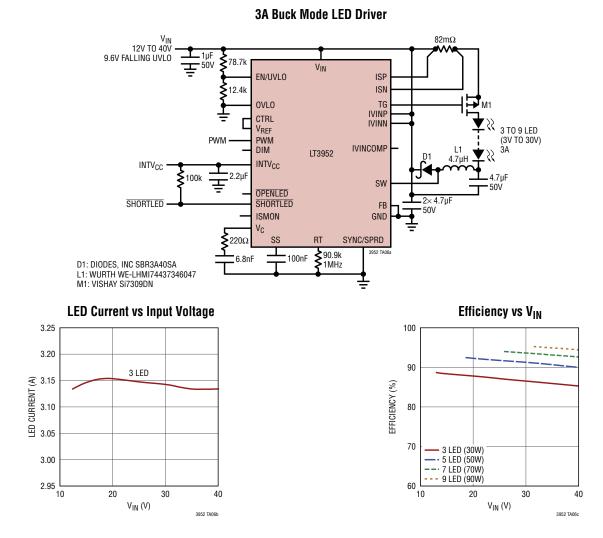

#### Short-Circuit Robust Boost LED Driver with Spread Spectrum Frequency Modulation

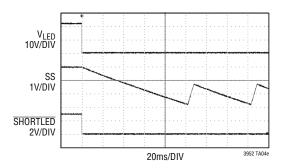

#### Short LED Protection without $R_{\mbox{\scriptsize SS}}$ : Hiccup Mode

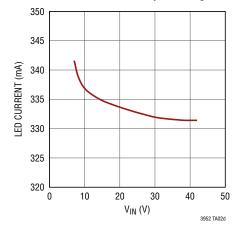

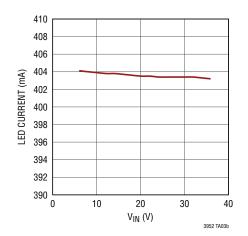

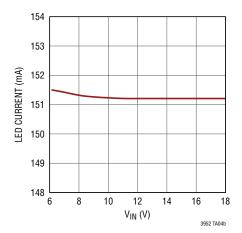

**LED Current vs Input Voltage**

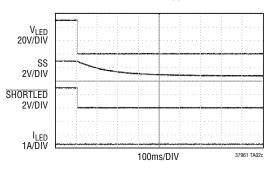

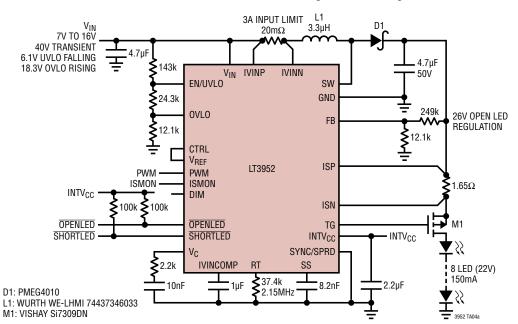

#### Short LED Protection with R<sub>SS</sub>: Latchoff Mode