# **i.MX53 Quick Start Board** Take your Multimedia Experience to the max

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

**Learn More:** For more information about Freescale products, please visit www.freescale.com.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011. All rights reserved.

## Hardware Reference Manual for i.MX53 Quick Start

### **Table of Contents**

| 1. | Intro | roduction1                                   |    |  |

|----|-------|----------------------------------------------|----|--|

|    | 1.1.  | i.MX53-QUICK START Board Overview            | 1  |  |

|    | 1.2.  | i.MX53-QUICK START Board Kit Contents        | 2  |  |

| 2. | List  | of Acronyms                                  | 3  |  |

| 3. | Spe   | cifications                                  | 4  |  |

|    | 3.1.  | i.MX535 Processor                            | 4  |  |

|    | 3.2.  | DDR3 DRAM Memory                             | 7  |  |

|    | 3.3.  | Dialog DA9053 PMIC                           | 7  |  |

|    | 3.4.  | MicroSD Card Slot (J4)                       | 8  |  |

|    | 3.5.  | SD Card Slot (J5)                            | 8  |  |

|    | 3.6.  | SATA 7-pin Data Connector (J7)               | 8  |  |

|    | 3.7.  | VGA Video Output (J8)                        | 8  |  |

|    | 3.8.  | LVDS Video Output (J9)                       | 9  |  |

|    | 3.9.  | Ethernet (J2B)                               | 9  |  |

|    | 3.10. | Dual USB Host Connector (J2A)                | 9  |  |

|    | 3.11. | Micro-B USB Device Connector (J3)            | 10 |  |

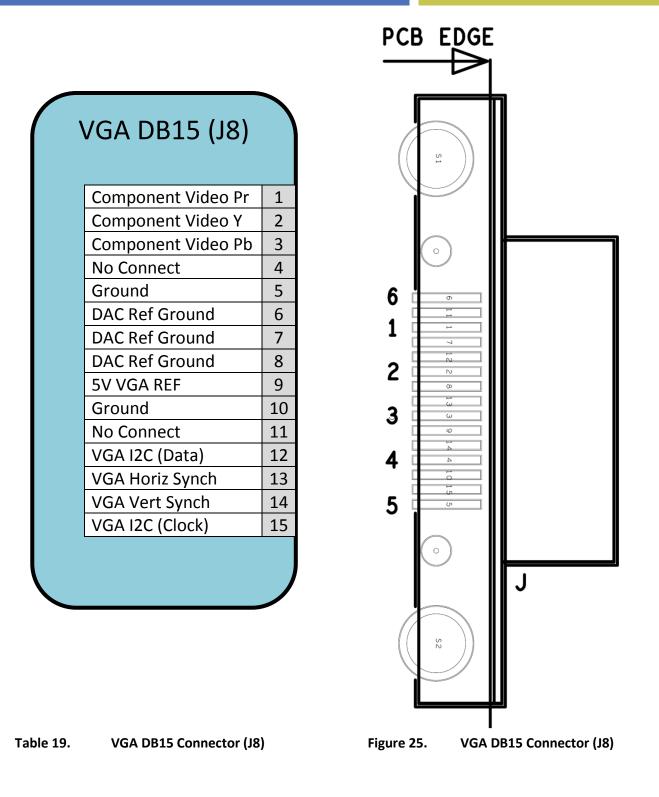

|    | 3.12. | Audio Input/Output (J6/J18)                  | 10 |  |

|    | 3.13. | 5V Power Connector (J1)                      | 10 |  |

|    | 3.14. | Debug UART Connector (J16)                   | 11 |  |

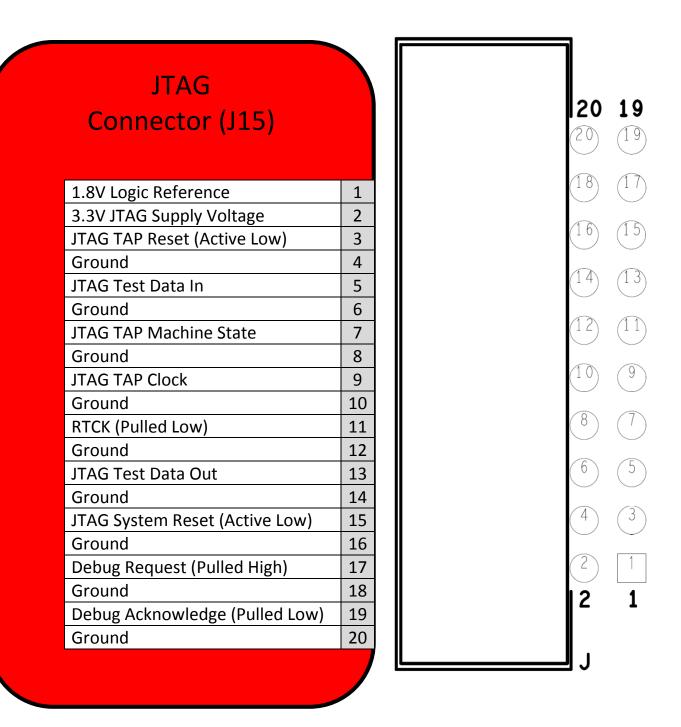

|    | 3.15. | JTAG Connector (J15)                         | 11 |  |

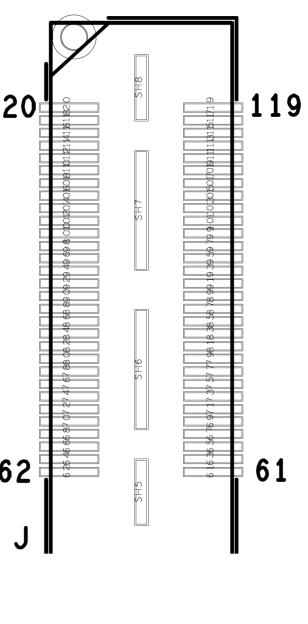

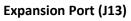

|    | 3.16. | Expansion Header (J13)                       | 12 |  |

|    | 3.17. | User Interface Buttons                       | 12 |  |

|    | 3.18. | User Interface LED Indicators                | 13 |  |

|    | 3.19. | Optional Li-ION Batter Connector (J14)       | 14 |  |

|    | 3.20. | Optional Back-Up Coin Cell posts (JP1, JP2)  | 14 |  |

|    | 3.21. | PCB Shorting Traces                          | 15 |  |

| 4. | Quio  | ck Start Board Connectors and Expansion Port | 15 |  |

|    | 4.1.  | Wall 5V Power Jack (J1)                      | 16 |  |

|    | 4.2.  | RJ45 Ethernet Connector (J2B)                | 17 |  |

|    | 4.3.  | VGA DB15 Connector (J8)                      | 18 |  |

|    | 4.4.  | Debug UART DB9 Connector (J16)               | 19 |  |

|    | 4.5.  | Headphone Output Connector (J18)             | 20 |  |

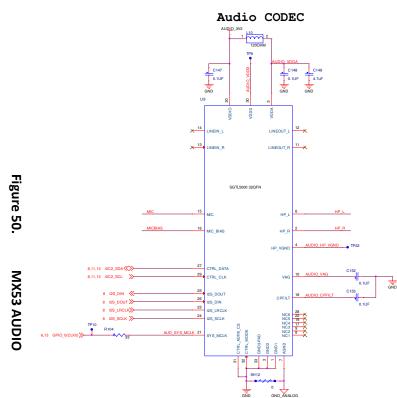

|    | 4.6.  | Microphone Input Connector (J6)              | 21 |  |

|    |       |                                              |    |  |

|    | 4.7.   | Dual USB Host Jack (J2)             |            |

|----|--------|-------------------------------------|------------|

|    | 4.8.   | micro-B USB Device Connector (J3)   |            |

|    | 4.9.   | SATA 7-pin Data Connector (J7)      |            |

|    | 4.10.  | SD Card Connector (J5)              |            |

|    | 4.11.  | microSD Card Connector (J3)         |            |

|    | 4.12.  | 20-pin ARM JTAG Connector (J15      | 5)         |

|    | 4.13.  | LVDS Connector (J9)                 |            |

| 5. | Quio   | k Start Board Architecture and Desi | gn29       |

|    | 5.1.   | 5V Power Supply                     |            |

|    | 5.2.   | Dialog DA9053 PMIC                  |            |

|    | 5.2.   | L. Quick Start Power Rails          |            |

|    | 5.2.   | 2. Li-ION Battery Charging          |            |

|    | 5.2.   | B. Backlight LED Driver             |            |

|    | 5.2.   | 1. Touch-Screen Operation           |            |

|    | 5.2.   | 5. Miscellaneous                    |            |

|    | 5.3.   | 3.2V Secondary Voltage Regulator    |            |

|    | 5.4.   | i.MX53 Applications Processor       |            |

|    | 5.4.   | L. Peripheral Module Logic Volta    | ge Levels  |

|    | 5.4.   | 2. Boot Mode Operations and Se      | lections41 |

|    | 5.4.   | 3. Clock Signals                    |            |

|    | 5.4.   | i.MX53 Internal Regulators          |            |

|    | 5.4.   | 5. Watch Dog Timer                  |            |

|    | 5.5.   | DDR3 SDRAM Memory                   |            |

|    | 5.6.   | Micro SD Card Connector             |            |

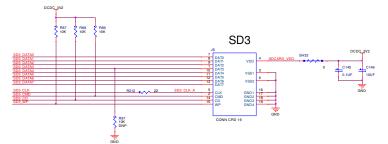

|    | 5.7.   | Full Size SD Card Connector         |            |

|    | 5.8.   | VGA Video Output                    |            |

|    | 5.9.   | LVDS Video Output                   | 55         |

|    | 5.10.  | Expansion Port                      |            |

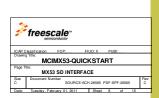

|    | 5.11.  | Audio                               |            |

|    | 5.12.  | Ethernet                            |            |

|    | 5.13.  | USB Host connections                |            |

|    | 5.14.  | SATA                                |            |

|    | 5.15.  | Debug UART Serial Port              | 61         |

|    | 5.16.  | JTAG Operations                     |            |

| 6. | Con    | nector Pin-Outs                     |            |

| Fr | eescal | e Semiconductor                     |            |

### Hardware Reference Manual for i.MX53 Quick Start

| 7. B | oard Accessories                 | 80 |

|------|----------------------------------|----|

| 7.1. | HDMI Daughter Card               | 80 |

| 7.2. | LCD Display Daughter Card        | 82 |

| 7.3. | LVDS Display Set (Coming Soon)   | 84 |

| 8. N | Iechanical PCB Information       | 86 |

| 9. B | oard Verification                | 88 |

| 10.  | Troubleshooting                  | 92 |

| 10.1 | L. PMIC Voltage Rail Test Points | 93 |

| 11.  | Known Issues                     | 95 |

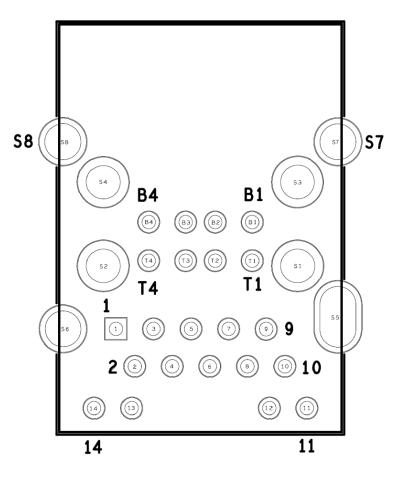

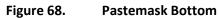

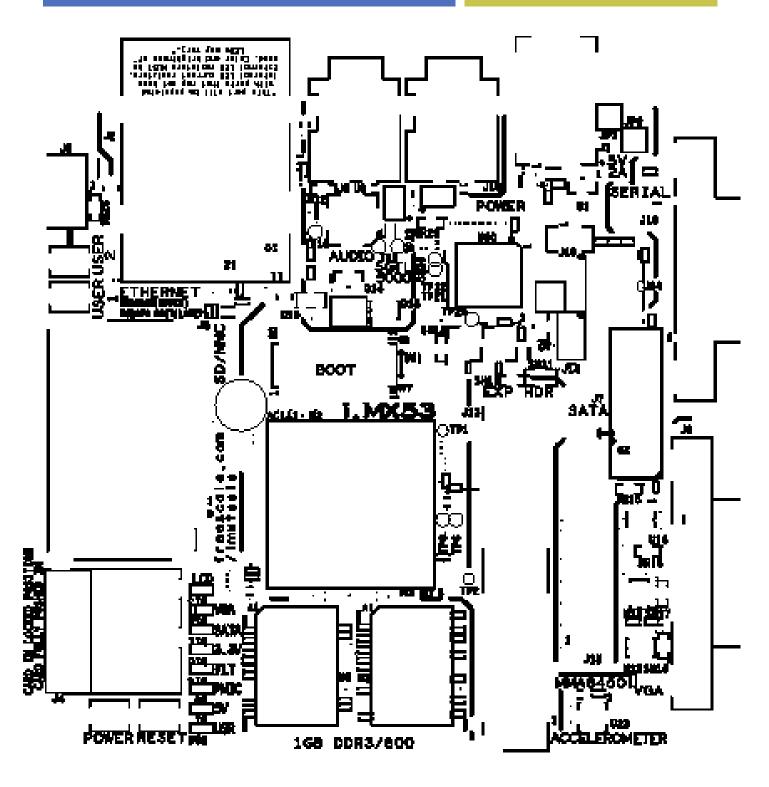

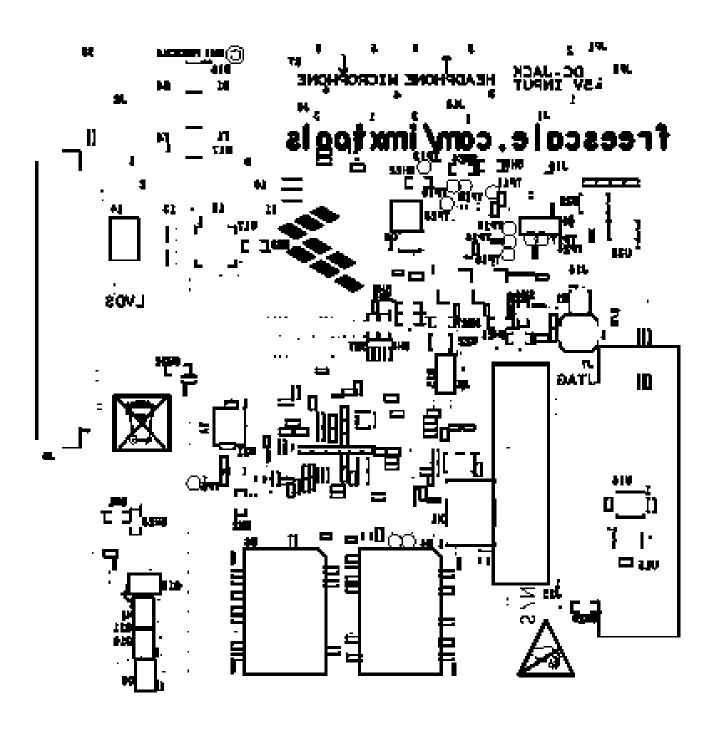

| 12.  | PCB Component Locations          | 96 |

| 13.  | Schematics                       | 01 |

| 14.  | Bill of Materials1               | 15 |

| 15.  | PCB information1                 | 22 |

#### List of Figures

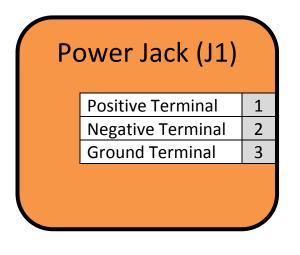

| Figure 1.  | DC Power Jack                               |    |

|------------|---------------------------------------------|----|

| Figure 2.  | RJ45 Ethernet Connector                     |    |

| Figure 3.  | VGA Connector                               |    |

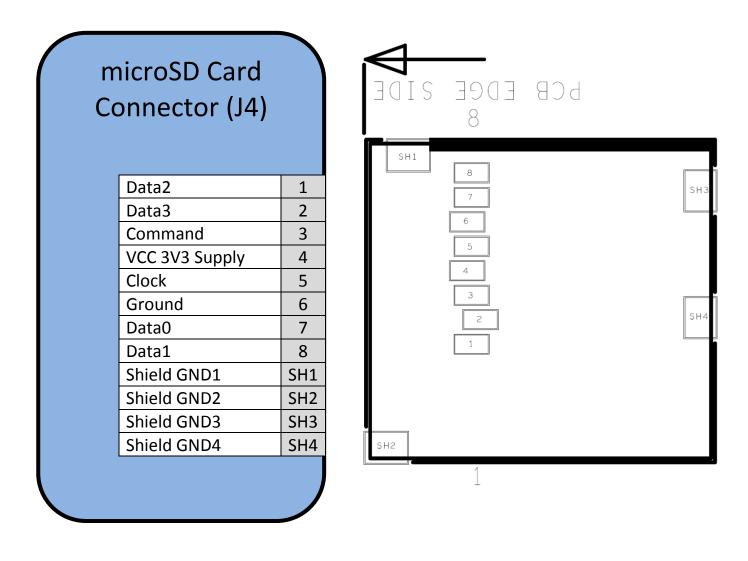

| Figure 4.  | Debug UART Connector                        | 19 |

| Figure 5.  | Headphone Output Connector                  | 20 |

| Figure 6.  | Microphone Connector (J6)                   |    |

| Figure 7.  | Dual USB Host Connectors (J2)               |    |

| Figure 8.  | micro-B USB Device Connector (J3)           |    |

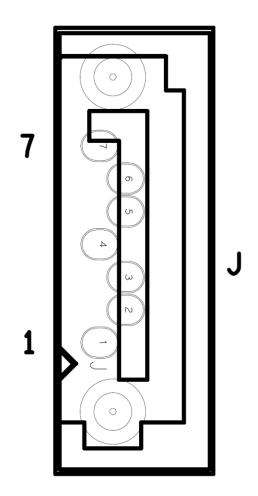

| Figure 9.  | SATA Data Connector (J7)                    |    |

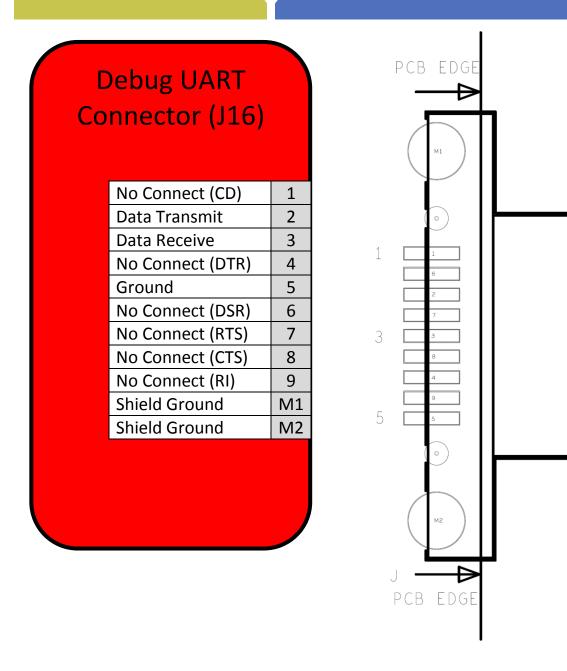

| Figure 10. | SD Card Connector (J5)                      |    |

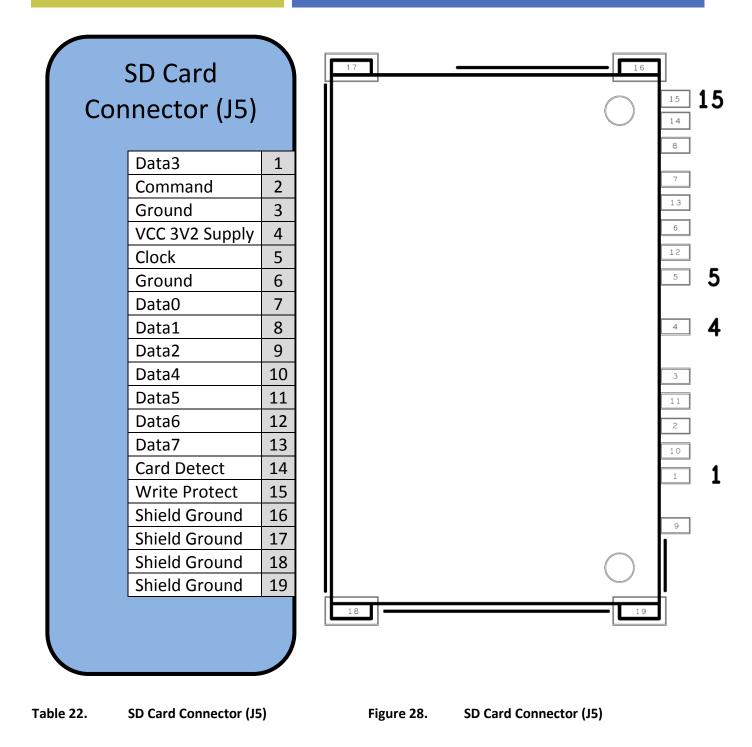

| Figure 11. | microSD Card Connector (J4)                 |    |

| Figure 12. | JTAG Connector (J15)                        |    |

| Figure 13. | LDVS Connector (J9)                         |    |

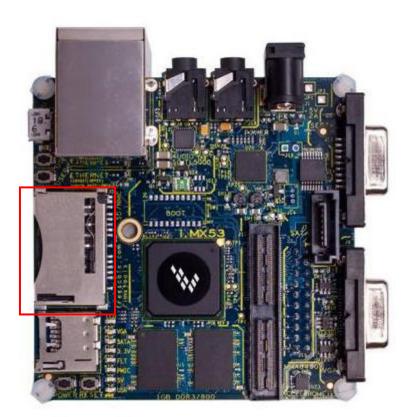

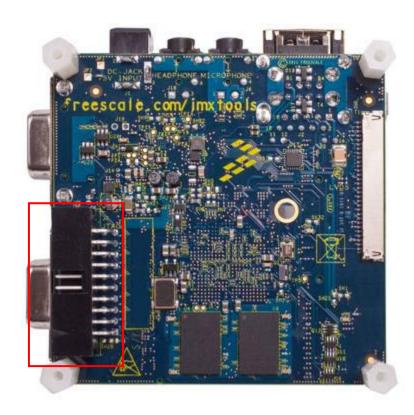

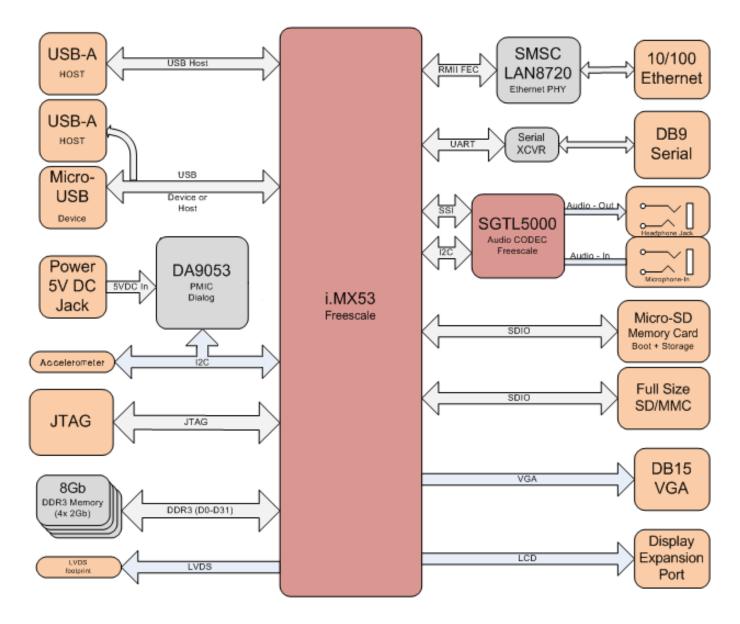

| Figure 14. | i.MX53 Smart-Start Block Diagram            | 29 |

| Figure 15. | Board Main Power Circuit.                   |    |

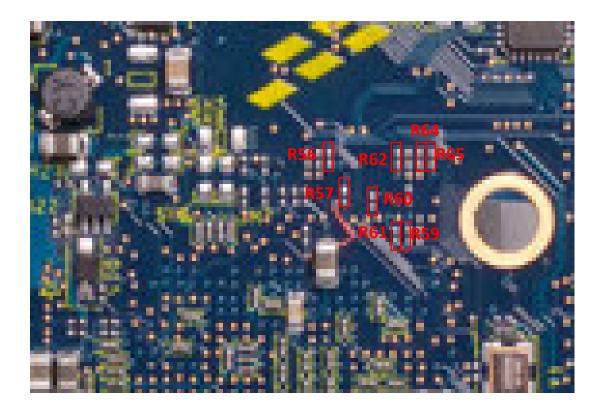

| Figure 16. | Boot Mode Resistor Locations TOP            |    |

| Figure 17. | Boot Mode Resistor Locations BOTTOM         |    |

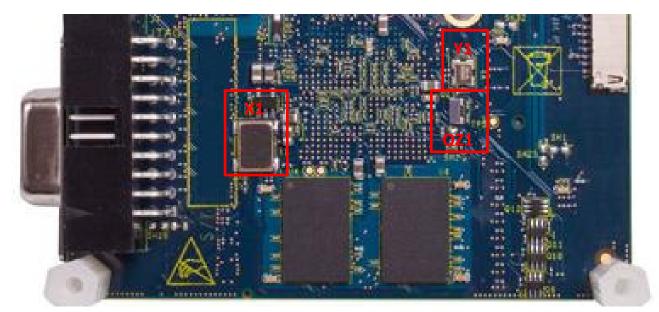

| Figure 18. | Clock Source Locations                      |    |

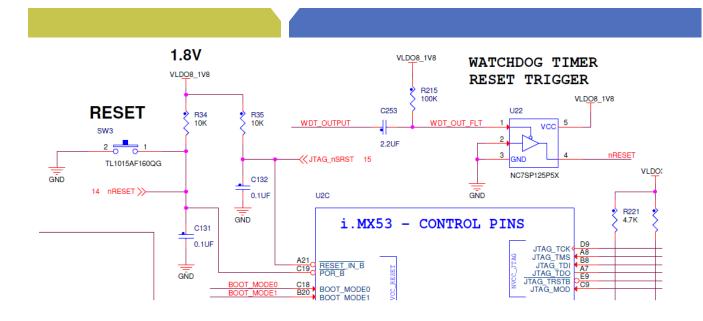

| Figure 19. | Watch Dog Timer Reset Trigger               |    |

| Figure 20. | Power Jack (J1)                             |    |

| Figure 21. | Micro-B USB Connector (J3)                  |    |

| Figure 22. | Ethernet/Dual USB Conn (J2)                 |    |

| Figure 23. | Headphone Connector (J18)                   |    |

| Figure 24. | Microphone Connector (J6)                   |    |

| Figure 25. | VGA DB15 Connector (J8)                     |    |

| Figure 26. | LVDS Connector (J9)                         |    |

| Figure 27. | SATA Data Connector (J7)                    |    |

| Figure 28. | SD Card Connector (J5)                      |    |

| Figure 29. | microSD Card Connector (J4)                 |    |

| Figure 30. | Debug UART Connector (J16)                  |    |

| Figure 31. | JTAG Connector (J15)                        |    |

| Figure 32. | Expansion Port (J13)                        | 74 |

| Figure 33. | Optional HDMI Daughter Card                 | 80 |

| Figure 34. | MCIMX28LCD 4.3" WVGA Display Daughter Card  |    |

| Figure 35. | LVDS Display Kit                            |    |

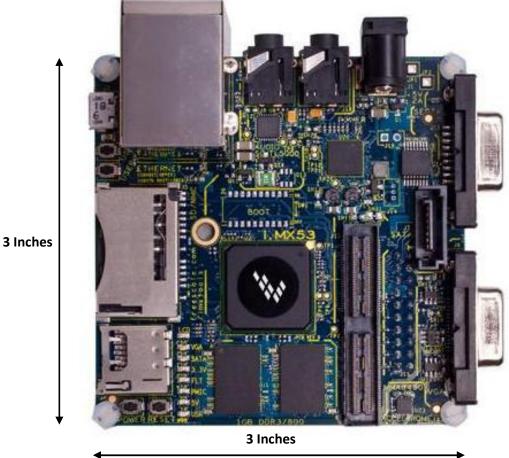

| Figure 36. | Quick Start Board Dimensions                |    |

| Figure 37. | Ethernet Loopback Cable                     |    |

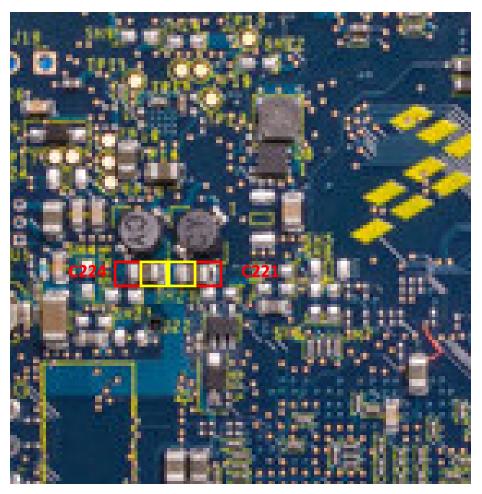

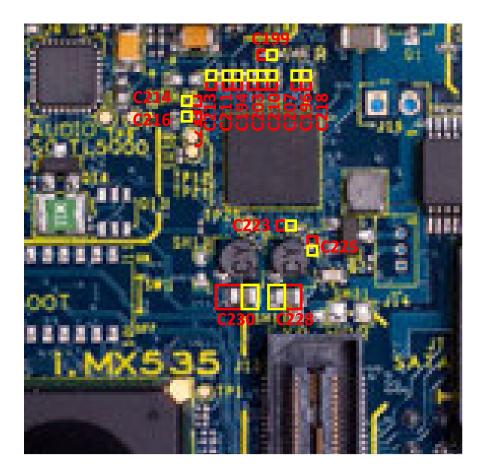

| Figure 38. | Regulator Output Capacitor Positions Bottom |    |

| Figure 39. | Regulator Output Capacitor Positions Top    |    |

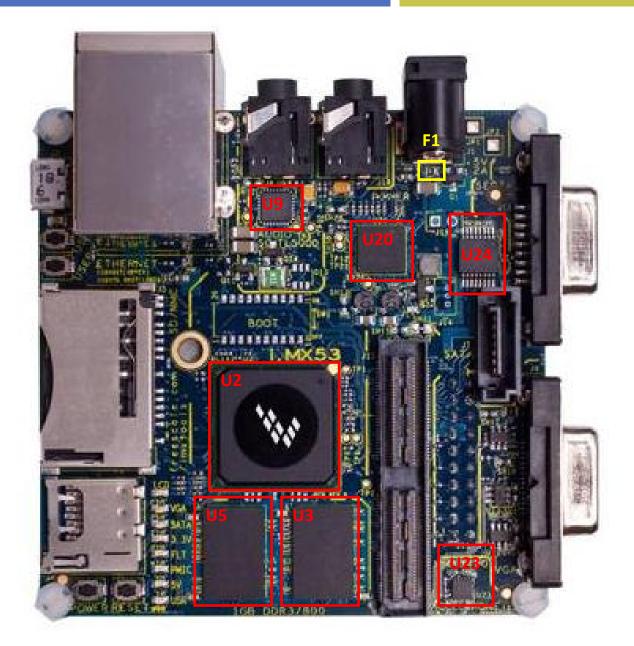

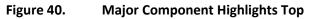

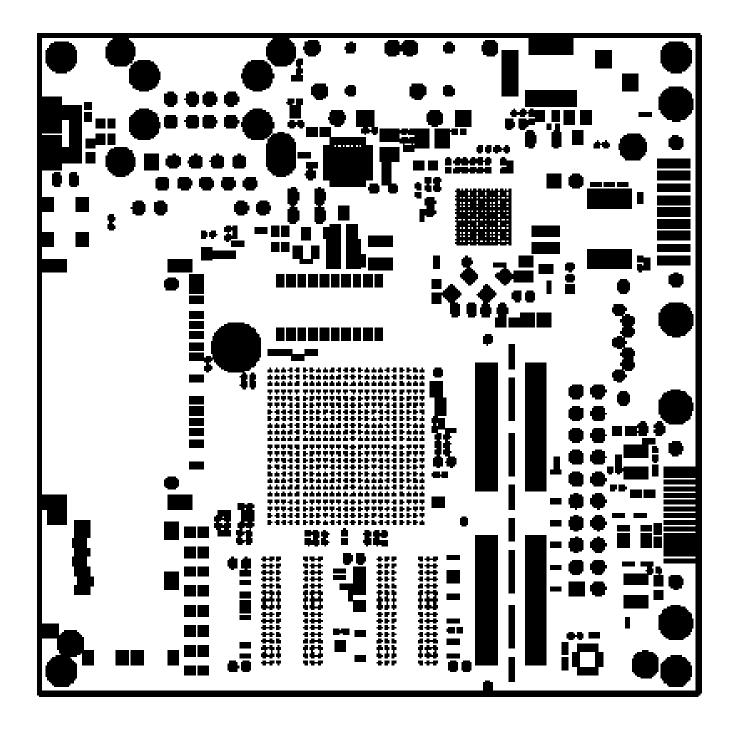

| Figure 40. | Major Component Highlights Top              |    |

#### List of Figures (con)

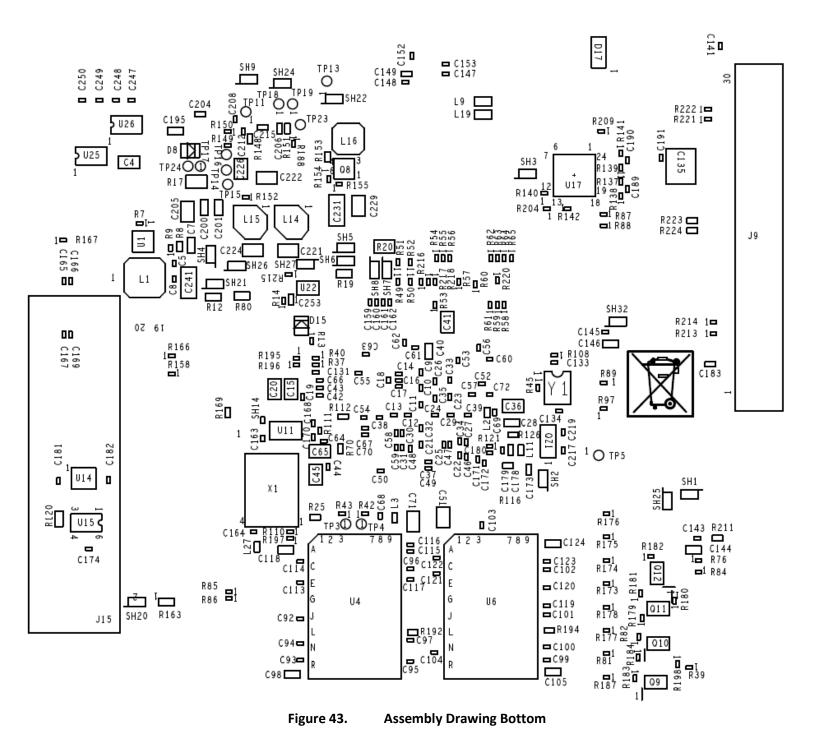

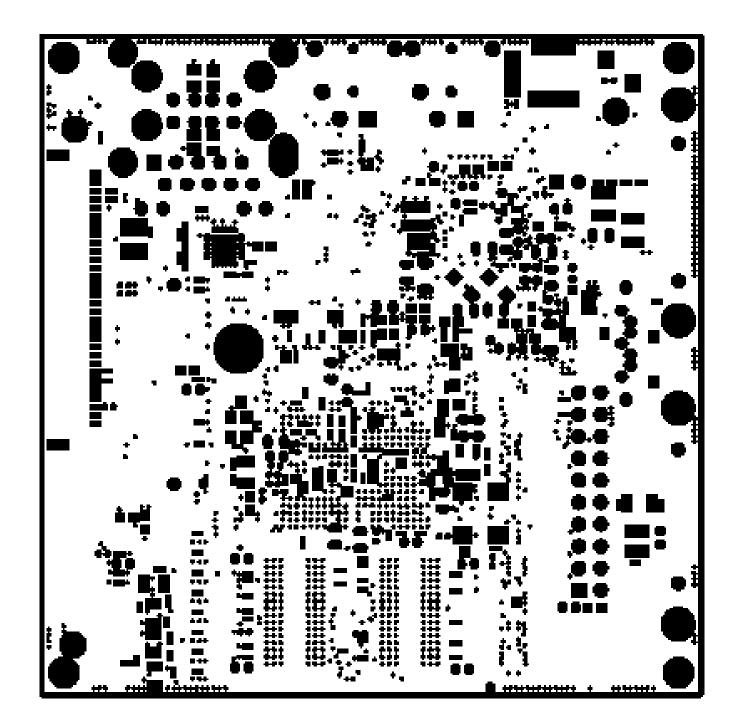

| Figure 41. | Major Component Highlights Bottom | 98   |

|------------|-----------------------------------|------|

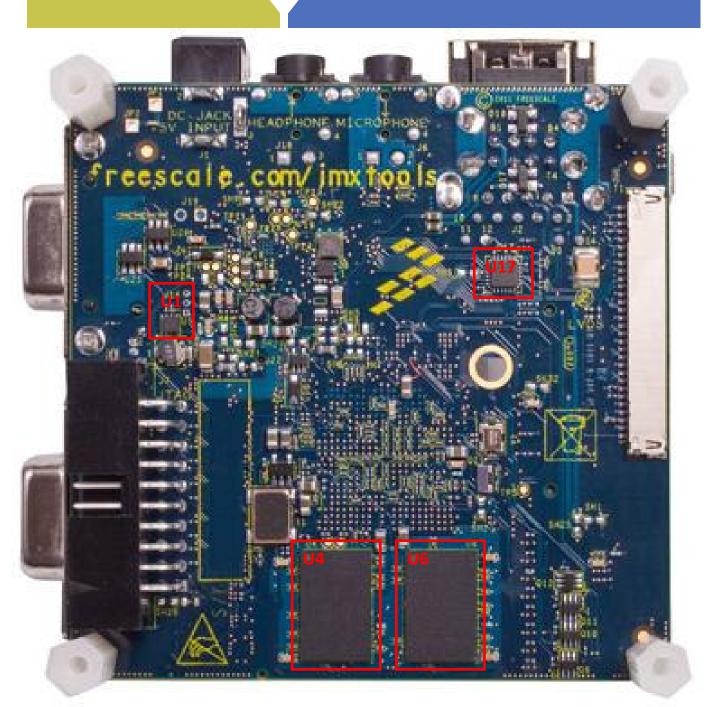

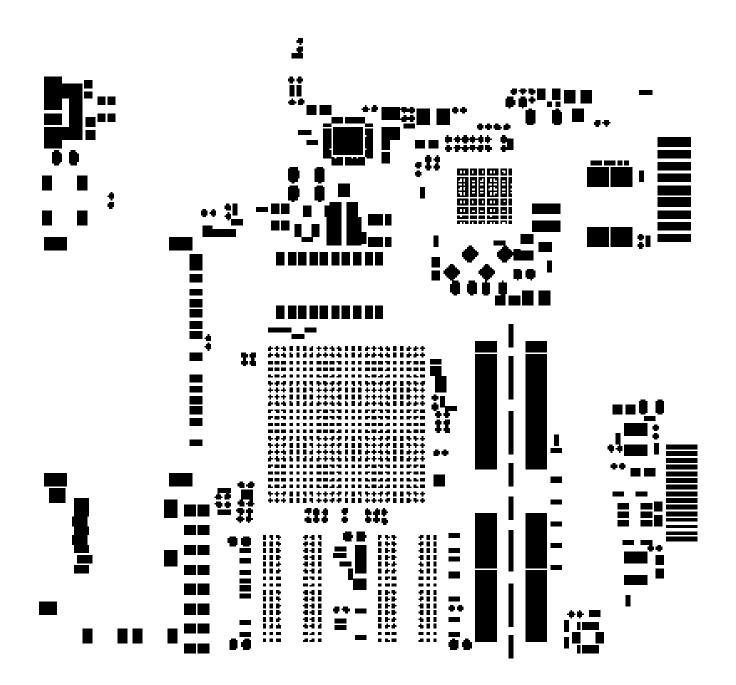

| Figure 42. | Assembly Drawing Top              | . 99 |

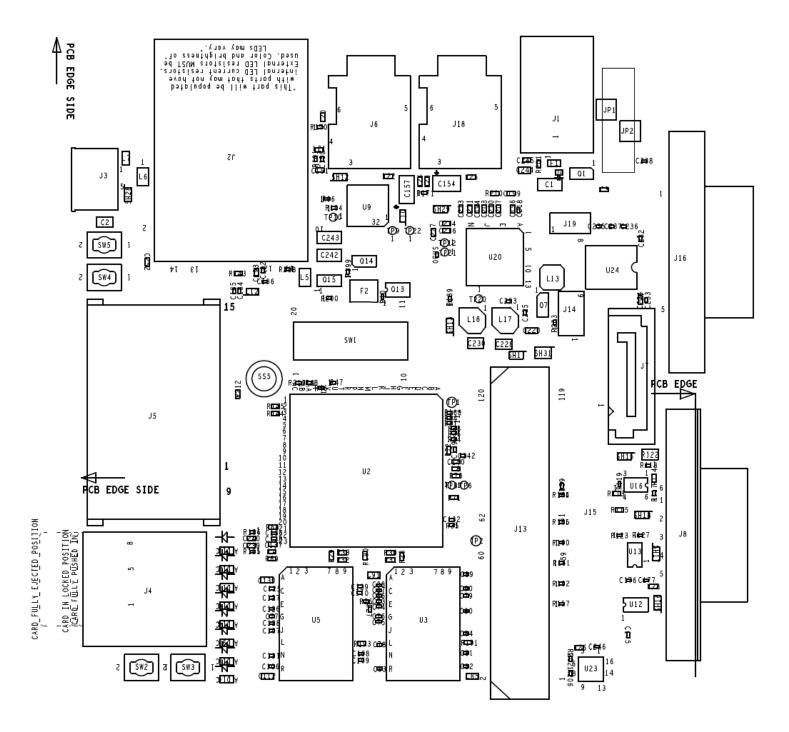

| Figure 43. | Assembly Drawing Bottom           | .100 |

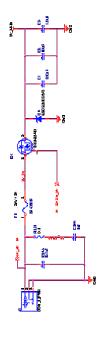

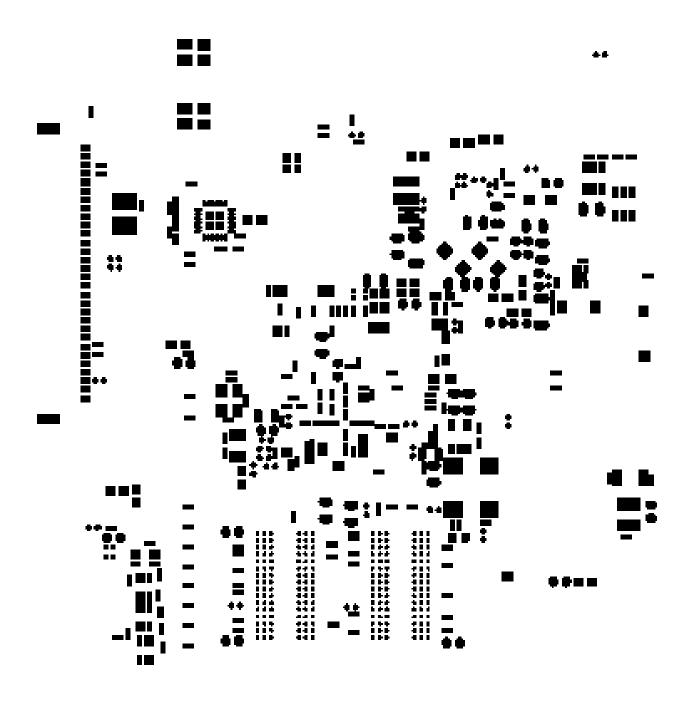

| Figure 44. | DC 5V INPUT                       | .102 |

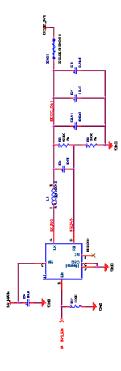

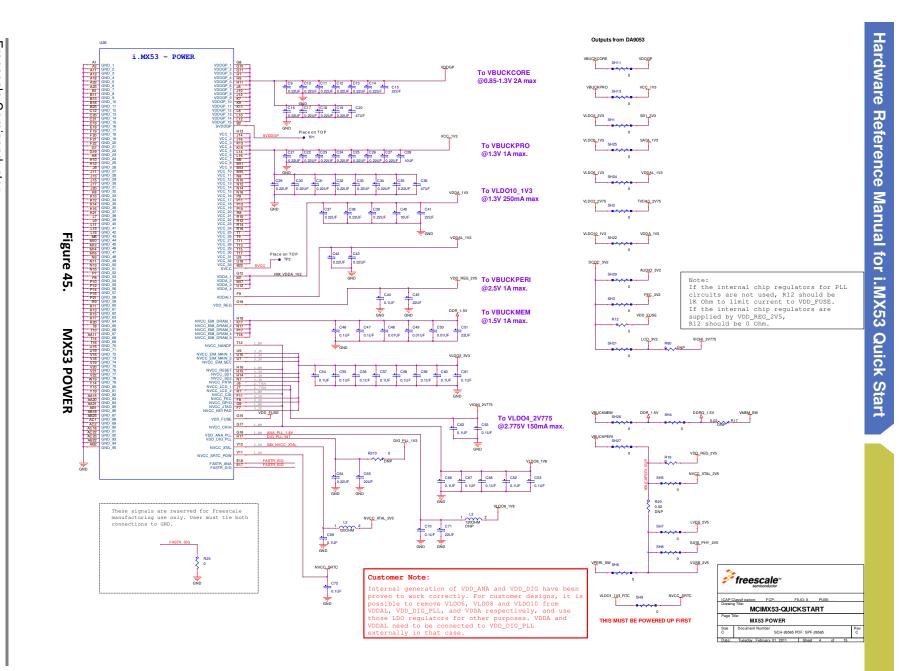

| Figure 45. | MX53 POWER                        | .103 |

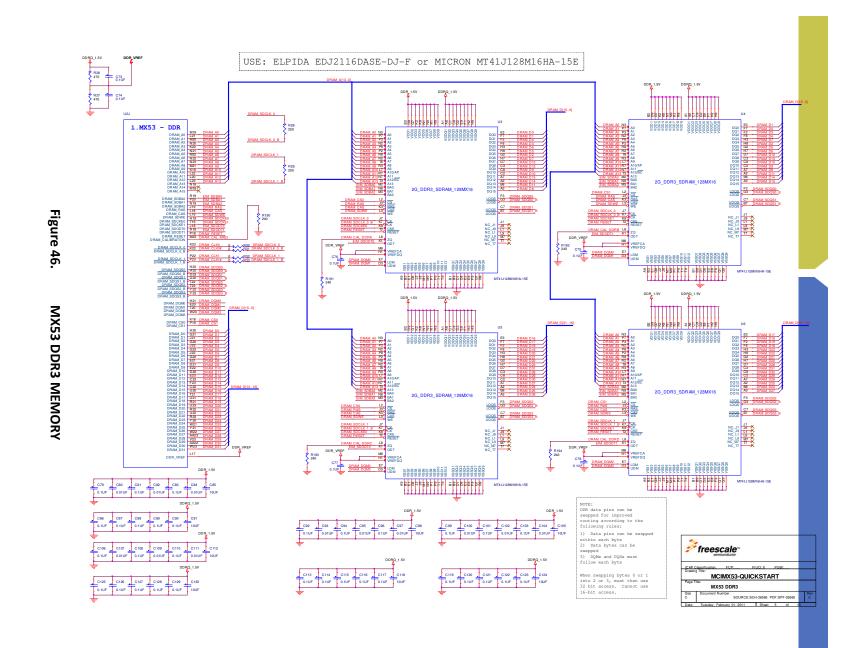

| Figure 46. | MX53 DDR3 MEMORY                  | 104  |

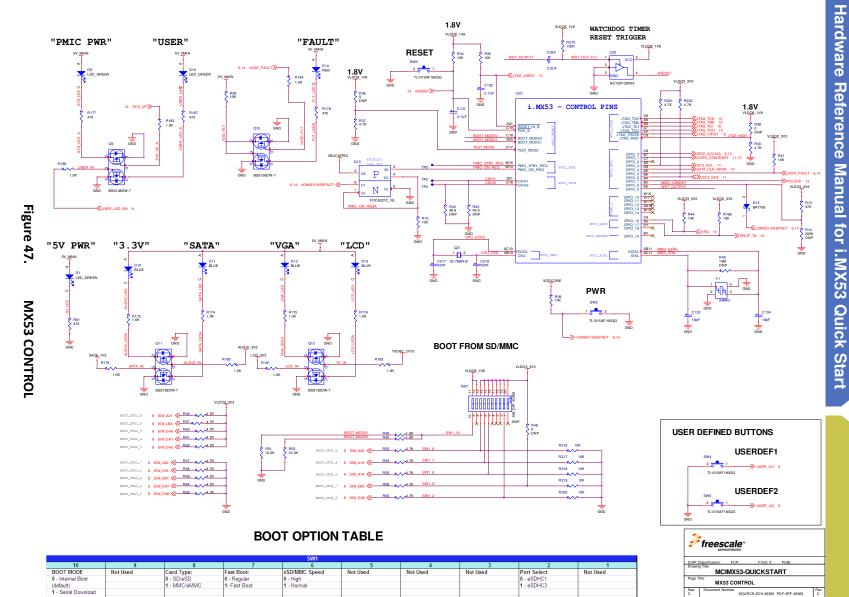

| Figure 47. | MX53 CONTROL                      | .105 |

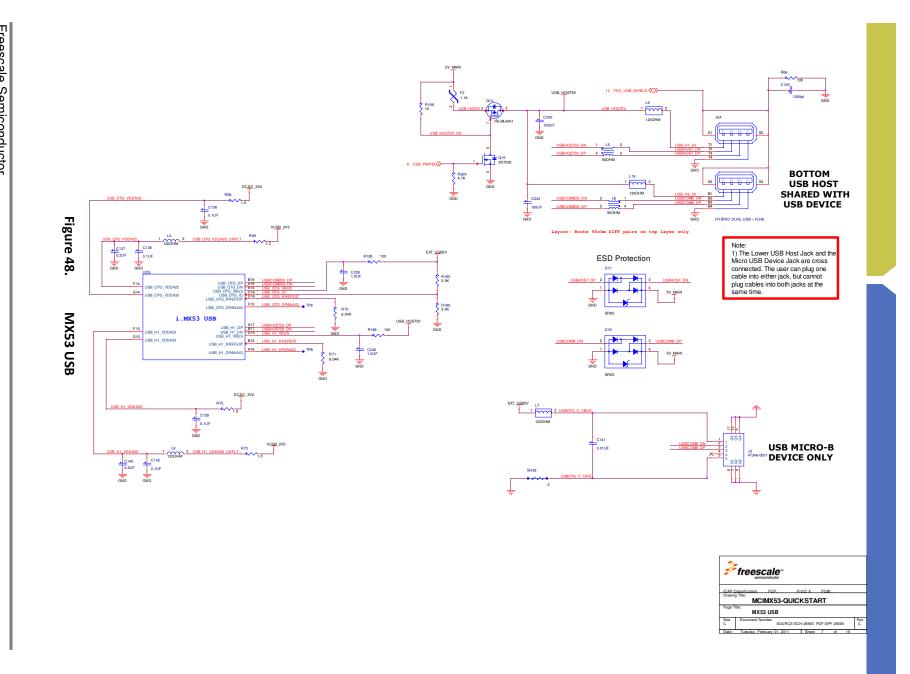

| Figure 48. | MX53 USB                          | .106 |

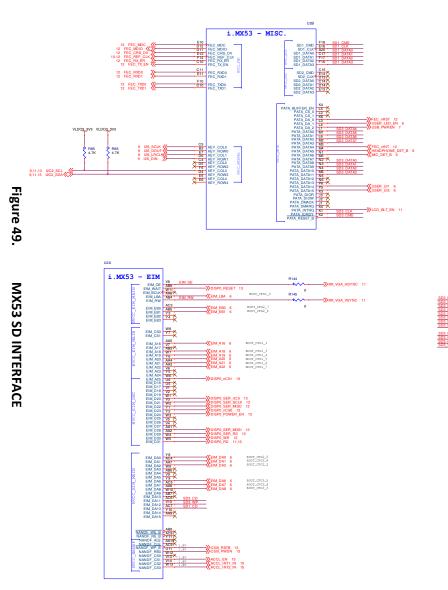

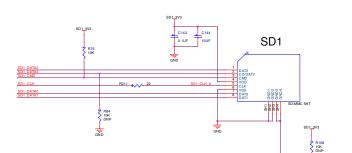

| Figure 49. | MX53 SD INTERFACE                 | .107 |

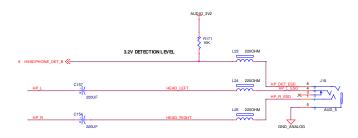

| Figure 50. | MX53 AUDIO                        | .108 |

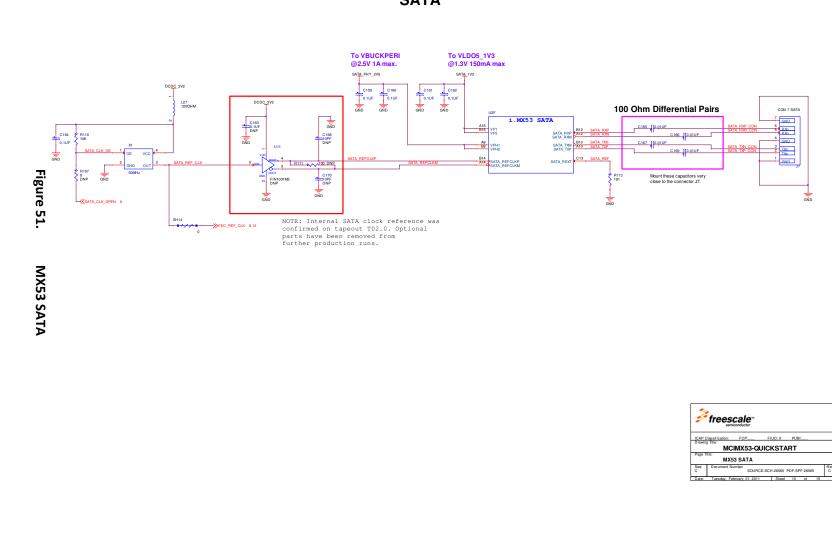

| Figure 51. | MX53 SATA                         | .109 |

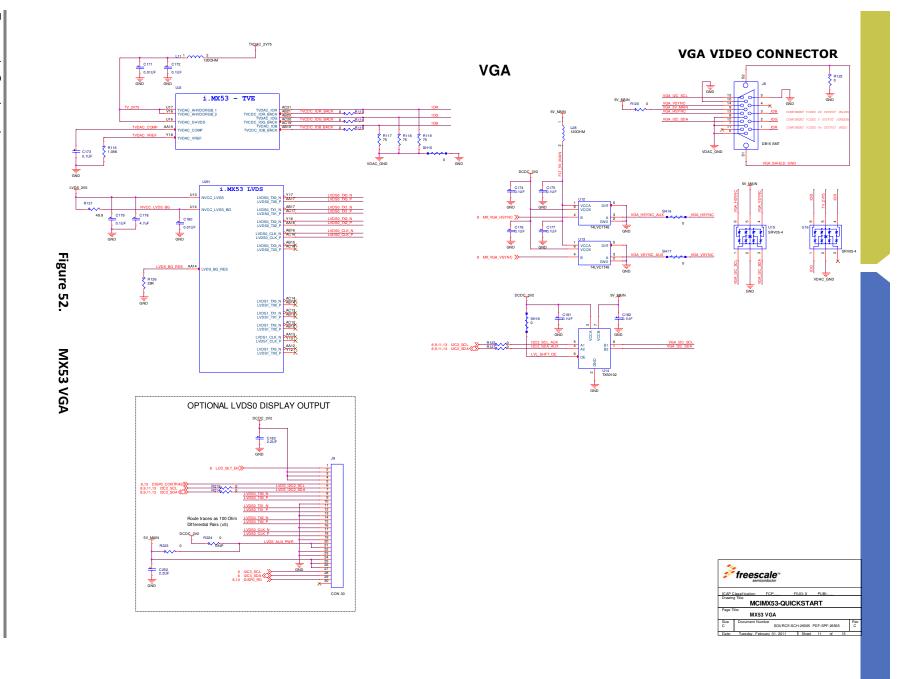

| Figure 52. | MX53 VGA                          | .110 |

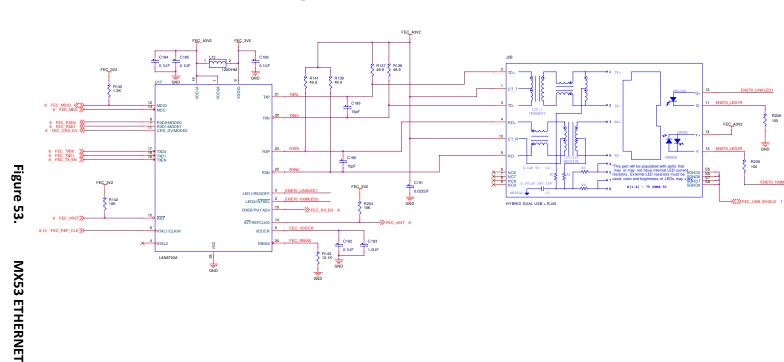

| Figure 53. | MX53 ETHERNET                     | 111  |

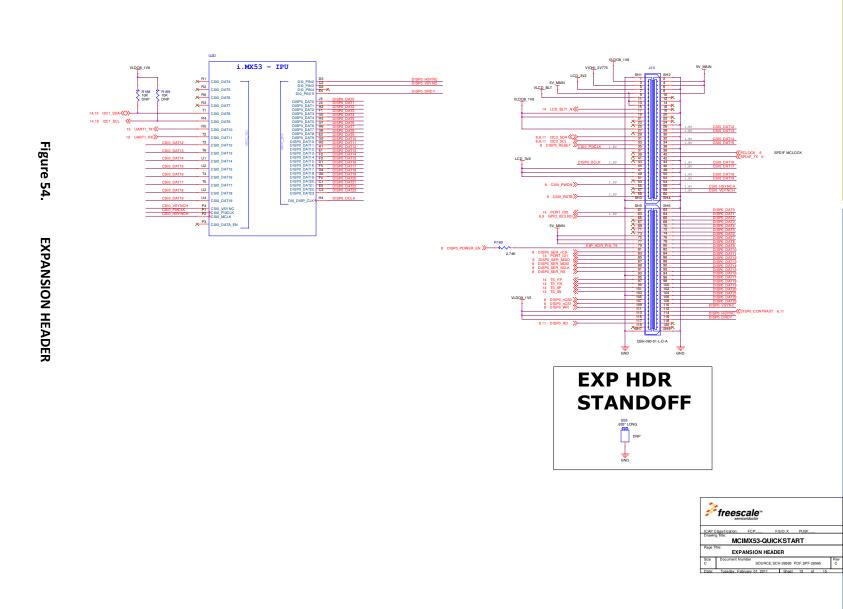

| Figure 54. | EXPANSION HEADER                  | .112 |

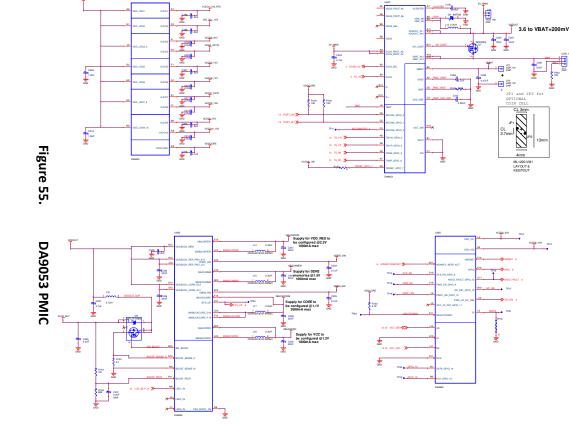

| Figure 55. | DA9053 PMIC                       | .113 |

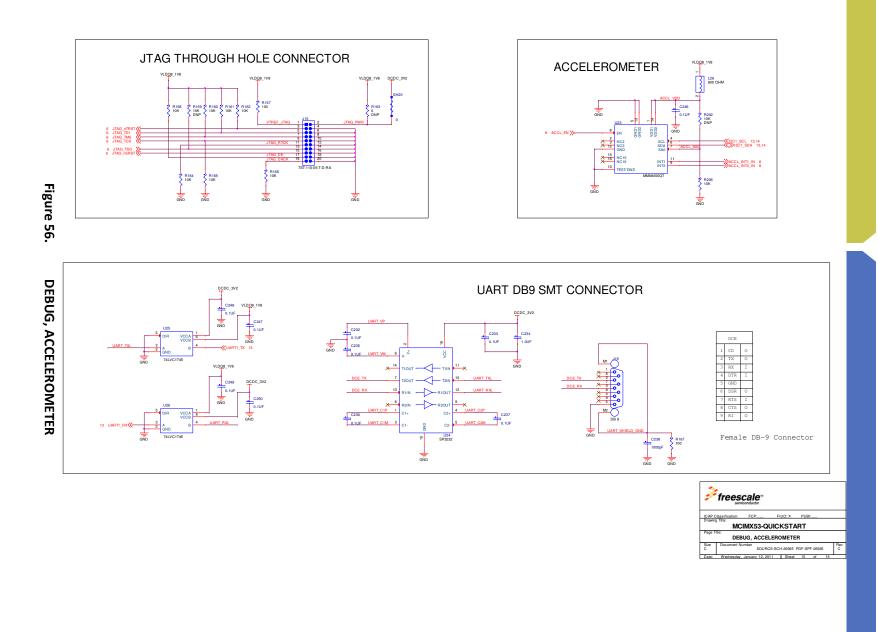

| Figure 56. | DEBUG, ACCELEROMETER              | .114 |

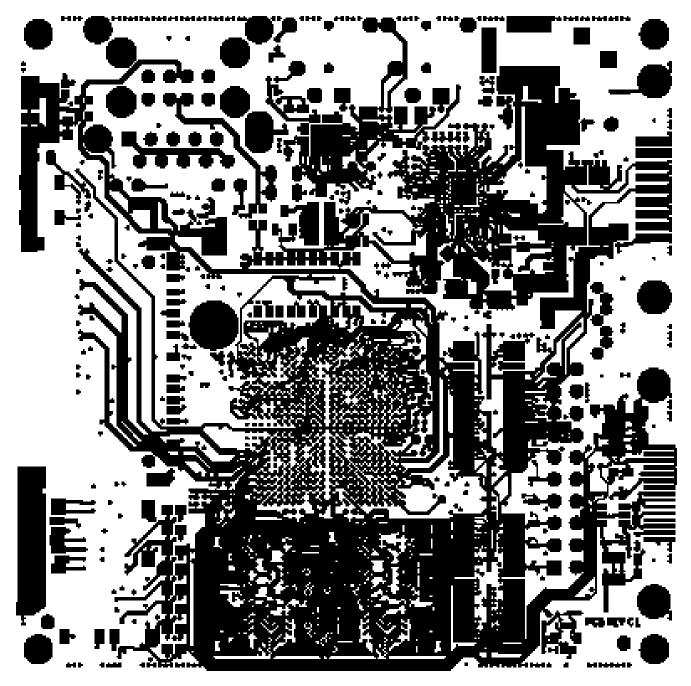

| Figure 57. | Top Etch Layer                    | .123 |

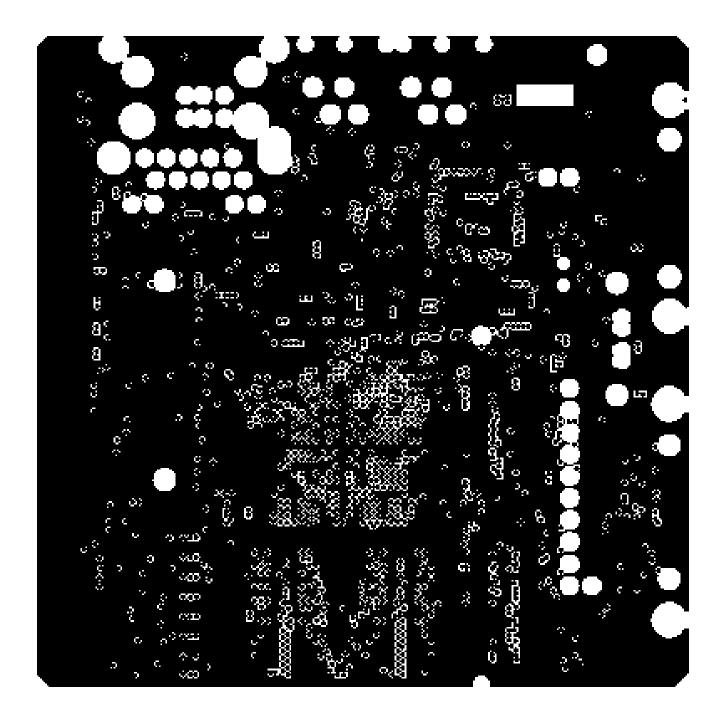

| Figure 58. | Second Etch Layer                 | .124 |

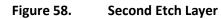

| Figure 59. | Third Etch Layer                  | .125 |

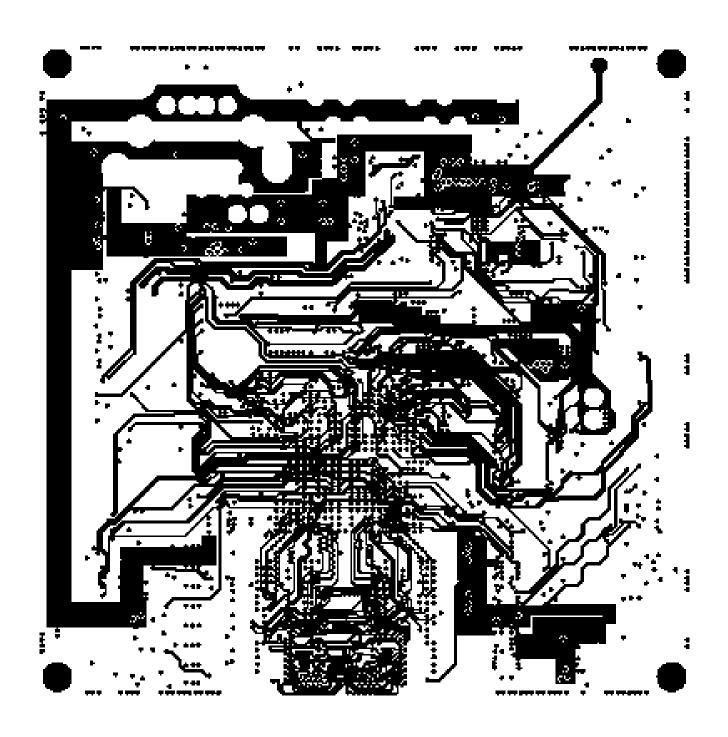

| Figure 60. | Fourth Etch Layer                 | 126  |

| Figure 61. | Fifth Etch Layer                  | .127 |

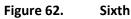

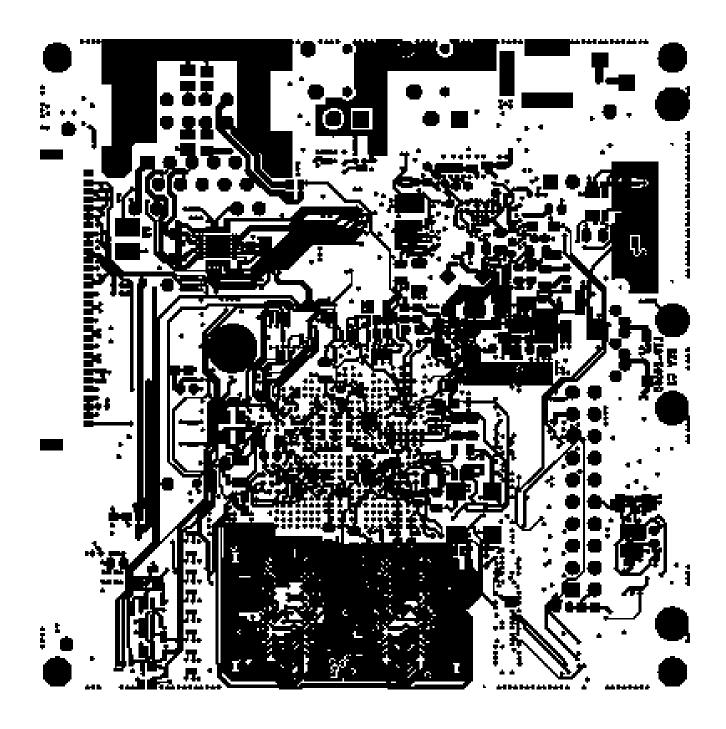

| Figure 62. | Sixth Etch Layer                  | .128 |

| Figure 63. | Seventh Etch Layer                | 129  |

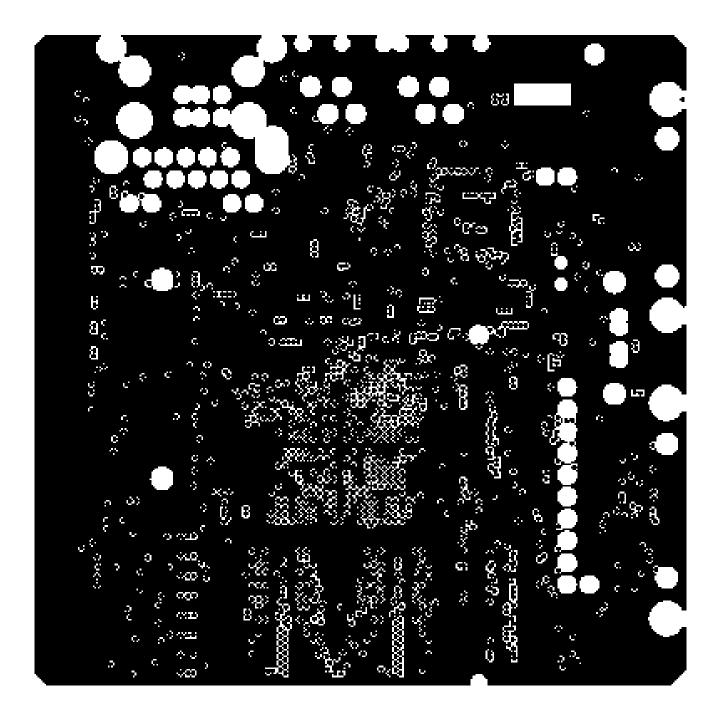

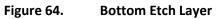

| Figure 64. | Bottom Etch Layer                 | 130  |

| Figure 65. | Soldermask Top                    | 131  |

| Figure 66. | Soldermask Bottom                 | .132 |

| Figure 67. | Pastemask Top                     | .133 |

| Figure 68. | Pastemask Bottom                  | 134  |

| Figure 69. | Silkscreen Top                    | 135  |

| Figure 70. | Silkscreen Bottom                 | .136 |

#### List of Tables

| Table 1.  | Regulator Timing Sequence            | .32  |

|-----------|--------------------------------------|------|

| Table 2.  | Quick Start Board Power Supply Rails | 33   |

| Table 3.  | Port ID Resistor Values              | 36   |

| Table 4.  | Module Voltage Supplies              | .40  |

| Table 5.  | BOOT_MODE pin Settings               | .41  |

| Table 6A. | BOOT_CFG Word1                       | . 41 |

| Table 6B. | BOOT_CFG Word2                       | . 41 |

| Table 6C. | BOOT_CFG Word3                       | . 42 |

| Table 7.  | Boot Mode Resistors TOP              | .46  |

| Table 8.  | Boot Mode Resistors BOTTOM           | . 47 |

| Table 9.  | DDR3 SDRAM Chip Organization         | . 51 |

| Table 10. | Micro-SD Card Boot Options           | 52   |

| Table 11. | Full Size SD Card Boot Options       | 53   |

| Table 12. | SATA Boot Mode Configuration Table.  | 60   |

| Table 13. | Terminal Setting Parameters          | 61   |

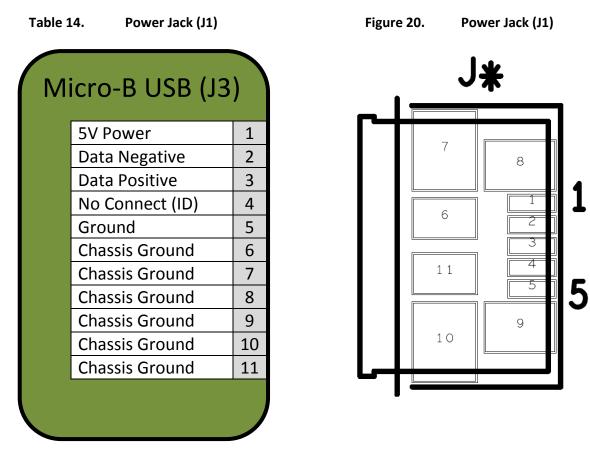

| Table 14. | Power Jack (J1)                      | 64   |

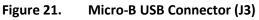

| Table 15. | Micro-B USB Connector (J3)           | . 64 |

| Table 16. | Ethernet/Dual USB Conn (J2)          | .65  |

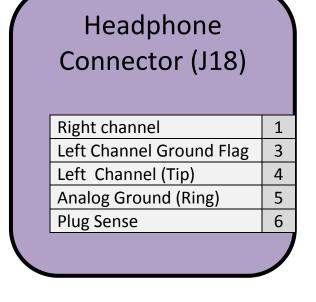

| Table 17. | Headphone Connector (J18)            | 66   |

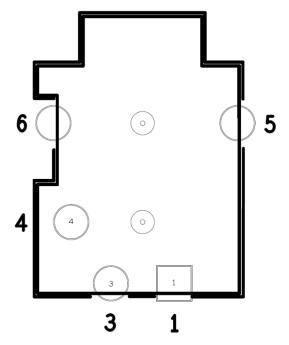

| Table 18. | Microphone Connector (J6)            | 66   |

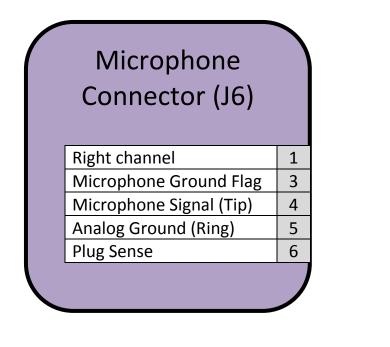

| Table 19. | VGA DB15 Connector (J8)              | 67   |

| Table 20. | LVDS Connector (J9)                  | 68   |

| Table 21. | SATA Data Connector (J7)             | 69   |

| Table 22. | SD Card Connector (J5)               | . 70 |

| Table 23. | microSD Card Connector (J4)          | 71   |

| Table 24. | Debug UART Connector (J16)           | 72   |

| Table 25. | JTAG Connector (J15)                 | 73   |

| Table 26. | Expansion Port (J13)                 | 74   |

| Table 27. | Expansion Port Pin-Mux Table         | . 76 |

| Table 28. | Board Stack up information           | . 87 |

| Table 29. | Problem Resolution Table             | . 92 |

| Table 30. | Output Capacitors and Values BOTTOM  | . 93 |

| Table 31. | Output Capacitors and Values TOP     | 94   |

### 1. Introduction

This document is the Hardware Reference Manual for the i.MX53 Quick Start board based on the Freescale Semiconductor i.MX53 Applications Processor. This board is fully supported by Freescale Semiconductor. This Manual includes system setup and debugging, and provides detailed information on the overall design and usage of the i.MX53 Quick Start board from a Hardware Systems perspective.

#### 1.1. i.MX53-QUICK START Board Overview

The Quick Start Board is an i.MX535 platform designed to showcase many of the most commonly used features of the i.MX535 Applications Processor in a small, low cost package. The MCIMX53-START is an entry level development board and a near perfect subset of its larger sister board, the MCIMX53SMD, which is available as a full, near-form factor tablet. Developers can start working with code on the Quick Start board, and then port it over to the SMD Tablet if additional features are desired. This gives the developer the option of becoming familiar with the i.MX535 Applications Processor before investing a large amount or resources in more specific designs. Features of the i.MX53 Quick Start board are:

| Processor:        | Freescale Applications Processor                                                                                                                                                             | MCIMX535DVV1B                               |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| DRAM Memory:      | Micron 8Gb DDR3 SDRAM                                                                                                                                                                        | MT41J128M16HA-187E:D                        |

| PMIC:             | Dialog Semiconductor                                                                                                                                                                         | DA9053                                      |

| Mass Storage:     | 5 in 1 SD/MMC/SDIO Card Connector<br>microSD Card Connector<br>7-pin SATA Data Connector                                                                                                     |                                             |

| Video Output:     | 15-Pin D-Sub VGA Connector<br>30-Pin LVDS Connector                                                                                                                                          |                                             |

| Ethernet:         | RJ-45 Connector for 10/100 Base-T                                                                                                                                                            |                                             |

| USB:              | Dedicated HS USB 2.0 Standard-A Host<br>Shared HS USB 2.0 Standard - Host and                                                                                                                |                                             |

| Audio Connectors: | 3.5mm Stereo Head Phone output<br>3.5mm Mono-Microphone input and N                                                                                                                          | Iono Head Phone (right channel) output      |

| Power Connectors: | 5V mm Barrel Connector                                                                                                                                                                       |                                             |

| Debug Connectors: | 9-Pin D-Sub Debug UART Connector<br>20-Pin Standard ARM JTAG Connector                                                                                                                       |                                             |

| Expansion Header: | 120-Pin Header (Populated) to Support<br>Optional HDMI Output Daughter Card (<br>Optional WVGA and WQVGA LCD Displ<br>Camera Daughter Card (custom)<br>SDIO Based WiFi Daughter card (custor | orderable)<br>ay Daughter Cards (orderable) |

| User Interface Buttons:   | Power, Reset, 2 User-Defined Buttons                                  |

|---------------------------|-----------------------------------------------------------------------|

| Indicators:               | 8 Status LEDs – External Power, PMIC ON, Fault Condition, and more    |

| Li-ION Battery Connector: | 3-Pin Header (unpopulated) for Li-ION Battery for Low Power Operation |

| Coin Cell:                | Connection point for 2-Pin Coin Cell (unpopulated) for RTC Operation  |

| PCB:                      | 3.0 inch x 3.0 inch (76.2 mm x 76.2 mm), 10 - layer board             |

#### 1.2. i.MX53-QUICK START Board Kit Contents

The i.MX53-Quick Start Board comes with the following items:

- ▶ i.MX53-QUICK START Board

- microSD Card preloaded with Ubuntu Demonstration Software

- USB Cable (Standard-A to Micro-B connectors)

- ➢ 5V/2.0A Power Supply

- Quick Start Guide

- Documentation DVD

#### 1.3. i.MX53 Quick Start Board Revision History

- Rev A Proof of Concept

- Rev B Prototype (Internal Freescale Development)

- Rev C Production (Silicon: i.MX53 Rev 2.0, DA9053 Rev AA)

The board version will be printed on a label, usually attached to the top of the SD Card Connector (J5). The board version will be the letter designation following the schematic revision:

#### SCH-26565 REV C

#### 2. List of Acronyms

The following acronyms will be used throughout this document.

| AC97   | - Audio Codec '97                                |

|--------|--------------------------------------------------|

| CMC    | - Common Mode Choke                              |

| CODEC  | - Compression/Decompression                      |

| DDR    | - Double Data Rate                               |

| DNP    | - Do Not Populate                                |

| HDMI   | - High Definition Multimedia Interface           |

| I2C    | - Inter-Integrated Circuit                       |

| 125    | <ul> <li>Integrated Interchip Sound</li> </ul>   |

| IC     | - Integrated Circuit                             |

| IDE    | <ul> <li>Integrated Debug Environment</li> </ul> |

| LAN    | - Local Area Network                             |

| LCB    | - i.MX53 Smart-Start                             |

| LCD    | -Liquid Crystal Display                          |

| LPDDR2 | - Low Power DDR2                                 |

| MMC    | - Multi Media Card                               |

| PMIC   | - Power Management Companion IC                  |

| RMII   | - Reduced Media Independent Interface            |

| RTC    | - Real-Time Clock                                |

| SDRAM  | - Synchronous Dynamic Random Access Memory       |

| SD     | - Secure Digital                                 |

| SPI    | - Serial Peripheral Interface                    |

| SSI    | - Synchronous Serial Interface                   |

| ULPI   | - UTMI Low Pin Interface                         |

| USB    | - Universal Serial Bus                           |

| UTMI   | - Universal Transceiver Macrocell Interface      |

| WDOG   | - Watch Dog                                      |

| WLAN   | - Wireless LAN                                   |

|        |                                                  |

### 3. Specifications

#### 3.1. i.MX535 Processor

The i.MX535 Applications Processor (AP) is based on ARM Cortex-A8<sup>™</sup> Platform, which has the following features:

- MMU, L1 Instruction and L1 Data Cache

- Unified L2 cache

- Target frequency of the core (including Neon, VFPv3 and L1 Cache): 1.0 GHz

- Neon coprocessor (SIMD Media Processing Architecture) and Vector Floating Point (VFP-Lite) coprocessor supporting VFPv3

- TrustZone

The memory system consists of the following components:

- Level 1 Cache:

- Instruction (32 Kbyte)

- Data (32 Kbyte)

- Level 2 Cache:

- Unified instruction and data (256 Kbyte)

- Level2 (internal) memory:

- Boot ROM, including HAB (64 Kbyte)

- Internal multimedia/shared, fast access RAM (128 Kbyte)

- Secure/non-secure RAM (16 Kbyte)

- External memory interfaces:

- 16/32-bit DDR2-800, LV-DDR2-800 or DDR3-800 up to 2 Gbyte

- 32 bit LPDDR2

- 8/16-bit NAND SLC/MLC Flash, up to 66 MHz, 4/8/14/16-bit ECC

- 16-bit NOR Flash. All WEIMv2 pins are muxed on other interfaces (data with NFC pins).

I/O muxing logic selects WEIMv2 port, as primary muxing at system boot.

- 16-bit SRAM, cellular RAM

- Samsung One NAND<sup>™</sup> and managed NAND including eMMC up to rev 4.4 (in muxed I/O mode)

The i.MX53 system is built around the following system on chip interfaces:

- 64-bit AMBA AXI v1.0 bus used by ARM platform, multimedia accelerators (such as VPU, IPU, GPU3D, GPU2D) and the external memory controller (EXTMC) operating at 200 MHz.

- 32-bit AMBA AHB 2.0 bus used by the rest of the bus master peripherals operating at 133 MHz.

- 32-bit IP bus peripheral bus used for control (and slow data traffic) of the most system peripheral devices operating at 66 MHz.

The i.MX53 makes use of dedicated hardware accelerators to achieve state-of-the-art multimedia performance. The use of hardware accelerators provides both high performance and low power consumption while freeing up the CPU core for other tasks.

#### Hardware Reference Manual for i.MX53 Quick Start

The i.MX53 incorporates the following hardware accelerator:

- VPU, version 3 video processing unit

- GPU3D 3D graphics processing unit, OpenGL ES 2.0, version 3, 33 Htri/s, 200 Mpix/s, and 800 Mpix/s z-plane performance, 256 Kbyte RAM memory.

- GPU2D 2D graphics accelerator, OpenVG 1.1, version 1, 200 Mpix/s performance.

- IPU, version 3M image processing unit

- ASRC asynchronous sample rate converter

The I.MX53 includes the following interfaces to external devices:

#### NOTE

Not all the interfaces are available simultaneously depending on I/O

multiplexer configuration.

- Hard disk drives:

- PATA, up to U-DMA mode 5, 100 MByte/s

- SATA II, 1.5 Gbps

- Displays:

- Five interfaces available. Total rate of all interfaces is up to 180 Mpixels/s, 24 bpp. Up to two interfaces may be active as once.

- Two parallel 24-bit display ports. The primary port is up to 165 Mpix/s (for example, UXGA @ 60 Hz).

- LVDS serial ports: one dual channel port up to 165 Mpix/s or two independent single channel ports up to 85 MP/s (for example, WXGA @ 60 Hz) each.

- TV-out/VGA port up to 150 Mpix/s (for example, 1080p60).

- Camera sensors:

- Two parallel 20-bit camera ports. Primary up to 180-MHz peak clock frequency, secondary up to 120-MHz peak clock frequency.

- Expansion cards:

- Four SD/MMC card ports: three supporting 416 Mbps (8-bit i/f) and one enhanced port supporting 832 Mbps (8-bit, eMMC 4.4)

- USB

- High-speed (HS) USB 2.0 OTG (up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- High-speed host with integrated on-chip high speed PHY

- Two high-speed hosts for external HS/FS transceivers through ULPI/serial, support IC-USB

- Miscellaneous interfaces:

- One-wire (OWIRE) port

- Three I2S/SSI/AC97 ports, supporting up to 1.4 Mbps, each connected to audio multiplexer (AUDMUX) providing four external ports.

- Five UART RS232 ports, up to 4.0 Mbps each. One supports 8-wire, the other four support 4-wire.

- Two high speed enhanced CSPI (ECSPI) ports plus one CSPI port

- Three I2C ports, supporting 400 kbps.

- Fast Ethernet controller, IEEE1588 V1 compliant, 10/100 Mbps

- Two controller area network (FlexCAN) interfaces, 1 Mbps each

- Sony Philips Digital Interface (SPDIF), Rx and Tx

- Enhanced serial audio interface (ESAI), up to 1.4 Mbps each channel

- Key pad port (KPP)

- Two pulse-width modulators (PWM)

- GPIO with interrupt capabilities

- Secure JTAG controller (SJC)

The system supports efficient and smart power control and clocking:

- Supporting DVFS (Dynamic Voltage and Frequency Scaling) and DPTC (Dynamic Process and Temperature Compensation) techniques for low power modes.

- Power gating SRPG (State Retention Power Gating) for ARM core and Neon

- Support for various levels of system power modes.

- Flexible clock gating control scheme

- On-chip temperature monitor

- On-chip oscillator amplifier supporting 32.768 kHZ external crystal

- On-chip LDO voltage regulators for PLLs

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, and so on)

- Secure JTAG controller (SJC) Protecting JTAC from debug port attacks by regulating or blocking the access to the system debug features.

- Secure real-time clock (SRTC) Tamper resistant RTC with dedicated power domain and mechanism to detect voltage and clock glitches.

- Real-time integrity checker, version 3 (RTICv3) RTIC type 1, enhanced with SHA-256 engine

- SAHARAv4 Lite Cryptographic accelerator that includes true random number generator (TRNG)

- Security controller, version 2 (SCCv2) Improved SCC with AES engine, secure/nonsecure RAM and support for multiple keys as well as TZ/non-TZ separation.

- Central Security Unit (CSU) Enhancement for the IIM (IC Identification Module). CSU is configured during boot and by e-fuses and determines the security level operation mode as well as the TrustZone (TZ) policy.

- Advanced High Assurance BOOT (A-HAB) HAB with the next embedded enhancements: SHA-256, 2046-bit RSA key, version control mechanism, warm boot, CSU and TZ initialization.

#### 3.2. DDR3 DRAM Memory

The i.MX53-Quick Start board uses four 2-Gigabit DDR3 SDRAM ICs manufactured by Micron for a total onboard RAM memory of 1 GigaByte. The SDRAM data width for each IC is 16-bits. The chips are arranged in pairs that are controlled by each of the two chip select pins to form 32-bit words for the i.MX53 CPU. On Die Termination (ODT) functionality has been implemented on the board, as well as the ability to separate out the I/O Voltage Supply from the main SDRAM Voltage Supply if desired.

#### 3.3. Dialog DA9053 PMIC

The DA9053 device is a small (7 x 7 mm, 0.5mm pitch) 169 ball VFBGA that provides nearly all power supply functions for the Quick Start board. The following is a feature list of the major functionality provided by the DA9053 PMIC for the Quick Start board:

- Power Supply resources:

- o 12 Low Drop Out (LDO) regulators

- 1 for internal PMIC purposes only (LDOCORE)

- 1 for charging optional back up coin cell

- 10 for platform needs

- 4 DC/DC Buck Converters (3 with DVS)

- 1 for the ARM Core supply (VBUCKCORE)

- 1 for the Peripheral Core supply (VBUCKPRO)

- 1 for the external SDRAM memory (VBUCKMEM)

- 1 for the internal cache memory (VBUCKPERI)

- 1 White LED driver and boost converter

- Li-ION battery Charger

0

- Resistive touch screen interface

- Expansion Port Card ID detect

- Wall voltage supply over-voltage protection

- 1 HS-I2C interface

- External LDO regulator enable

### 3.4. MicroSD Card Slot (J4)

The microSD Card slot is used as the primary means to boot the Quick Start board. The power source for the microSD Card slot is VLDO3\_3V3. The microSD Card slot is not normally configured with a card detect feature. The MicroSD Card slot can be configured to boot from a MMCmicro card with an alternate boot option setting (see section on Boot Options).

### 3.5. SD Card Slot (J5)

The SD Card slot is a 5-in-1 SD/MMC connector that acts as a secondary external memory media slot. The power source for the SD Card Slot is the auxiliary LDO regulator (DCDC\_3V2). The SD Card slot can be configured as the boot source with an alternate boot option setting, as well as being configured for either SD or MMC card operation (see section on Boot Options). The SD Card Slot supports full 8-bit parallel data transfers and can support SDIO cards (WiFi, BT, etc) designed to fit in a standard SD card slot. The Quick Start board has specifically been tested with an Atheros SD-25 WiFi card.

### 3.6. SATA 7-pin Data Connector (J7)

The SATA connector provides the means to connect an external SATA memory device to the Quick Start board. Commonly, this would be an External hard drive or a DVD/CD reader. Power for the SATA device needs to be supplied externally by the user via a 12-pin power connector. It is possible to boot from a SATA drive by making OTP fuse changes. Once the fuse changes are made, they cannot be reversed.

### 3.7. VGA Video Output (J8)

A standard VGA signal is output directly from the i.MX53 Processor with minimum external components required. Power for the TVE module of the i.MX535 Processor is supplied by VLDO7 of the PMIC and is set to 2.75V. If VGA output is not desired, it is possible to program the PMIC to turn off VLDO7 to conserve power. The VGA output supports a variety of video formats up to 150 Mega-Pixels per second. Level shifters are required on the Horizontal and Vertical Synchronization signals as well as the VGA I2C communications signals in order to meet VGA specifications.

#### 3.8. LVDS Video Output (J9)

The LVDS module of the i.MX53 Processor is connected to a 30-pin LVDS connector. While the i.MX53 Processor is capable of outputting to two separate LVDS displays, only one connector is pinned out on the Quick Start board. The pin outs on the LVDS connector match the optional cable and 10" HannStar LVDS display that can be purchased optionally from Freescale. The single LVDS connector will support video formats up to 165 Mega-Pixels per second. The power source for the LVDS module is a switchable output of the VBUCKPERI DCDC converter. This rail is shared with the SATA module and the USB module. If these modules are not being used, the PMIC can be programmed to turn off power to these three modules without affecting other 2.5V supplies to the remainder of the i.MX53 Applications Processor.

#### 3.9. Ethernet (J2B)

The i.MX53 Processor Fast Ethernet Module outputs RMII formatted signals to an external Ethernet PHY. The processor is capable of 10/100 Base-T speeds. The Quick Start board uses the SMSC LAN8720A Ethernet Transceiver in a QFN-24 package. 3.2V power is supplied to the Ethernet IC from the external LDO regulator. The output of the Ethernet PHY is connected to an RJ45 jack with integrated magnetic.

#### 3.10. Dual USB Host Connector (J2A)

The USB module of the i.MX53 Processor provides two high speed USB PHYs that are connected to each of the USB-A Host Jacks on connector J2. One PHY provides Host-only functionality and is connected to the upper USB jack on the connector tower. The second PHY is USB 2.0 OTG capable and is connected to the lower USB jack on the connector tower. Both jacks receive 5V power directly from the 5V Wall Power Supply, via a FET that can be controlled by software, and a 1.1A Poly-fuse. The PMIC provides an over-voltage functionality to limit voltage applied to the USB jack in the event that a DC Power Supply other than the original supply provided is used. Also, there is no current regulating device to limit current supplied to each jack, other than the Poly-fuse.

#### NOTE

The lower USB Host Jack is cross connected with the Micro-B USB Device connector. This was done as a convenience to the user as cables with micro-A plugs are still uncommon at the time the board was designed. The USB OTG PHY will switch to 'device' mode if a USB Host is attached to the micro-B connector with a cable. This design is not recommended for release to the general electronics consumer population. This board has not been tested for USB compliance.

### 3.11. Micro-B USB Device Connector (J3)

The micro-B USB connector is connected to the USB OTG PHY on the i.MX53 Processer, and is also connected to the Lower USB Host Jack on the connector tower. The connector's external USB 5V power pin is connected to the USB\_OTG\_ID pin, which is normally pulled to ground via a 3.3K Ohm resistor. When a powered USB Host device is attached to the micro-B USB connector, the USB\_OTG\_ID pin is pulled high and sends a signal to the USB OTG PHY to operate in device mode. The connector's external USB 5V power pin is not connected to the PMIC, or any other power rails on the Quick Start board. Therefore, it is not possible to supply power to the Quick Start board via the USB connections.

### 3.12. Audio Input/Output (J6/J18)

Analog audio input and output are provided by Freescale's Low Power Stereo Codec, SGTL5000. The audio codec is connected to the i.MX53 Applications Processor via 4-wire I2S communications, utilizing the AUDMUX5 port of the processor. The audio codec's Headphone Amp provides up to 58 mW output to 16-Ohm headphones at a typical SNR of 98 dB and THD+N of -86 dB. Typical power consumption is 11.6 mW. In addition, the audio codec can perform several enhancements to the output including virtual surround, added bass and three different types of equalization. The Microphone Input module of the Stereo Codec is also used, with the microphone input connected to the tip pin of the Microphone Jack (J6). Microphone Bias voltage is applied on the Quick Start board and not as a separate connection to the Microphone Jack. If the user desires to use a combined microphone, mono headphone device, the ferrite bead on L25 can be moved to the L22 pads, redirecting the right channel output to the Microphone Jack. A 2.5mm to 3.5mm adapter may be necessary to convert the microphone, mono headphone device to fit the Microphone Jack. On both the Headphone Jack and Microphone jack, a fourth pin is used to detect the insertion of a plug into either jack. When a standard 3-pin device is inserted into the 4-pin jack, the detect line is grounded, indicating to the i.MX53 Processor that the plug has been inserted.

### 3.13. 5V Power Connector (J1)

A 2.0mm x 6.5mm barrel connector is used which should fit standard DC Plugs with an inner dimension of 2.1mm and an outer dimension of 5.5mm. If an alternate power supply is used (not the original, supplied power supply), it should supply no more than 5.25V / 3A output. If the PMIC senses too high voltage at the connector input, it will turn off isolation FET Q1 to protect the Quick Start board. In between the Power Connector and the isolation FET is a single blow, fast acting fuse to protect the Quick Start board from an over current situation fault. If a Wall Power Supply is properly connected to the Quick Start board, and the green 5V power LED indicator is not lit, it could mean that either the fuse has been blown, or that the voltage output of the power supply is too high.

#### 3.14. Debug UART Connector (J16)

UART1 of the i.MX53 Processor is connected to an RS-232 output to be used as a debug output for the developer. The Transmit (TX) and Receive (RX) signals are sent through two 1.8V to 3.2V level shifters to convert the logic signal voltages to the correct values for the Sipex SP3232 RS-232 transceiver. The CTS and RTS signals are not used on the Quick Start board. The RS-232 transceiver receives its power from the external 3.2V LDO Regulator. If the output of the regulator is turned off for power savings measures, debug output will be lost.

If the designer wishes to use the port as an Applications UART Port, changes can be made in software to reconfigure the port. A male-to-male gender changer can be used to properly convert the port.

To access the debug data output during development, connect the Debug UART Connector to a suitable host computer and open a terminal emulation program (ie, Teraterm or HyperTerminal). Proper settings for the terminal program are:

- BAUD RATE: 115,200

- DATA: 8 bit

- PARITY: None

- STOP BIT: 1-bit

- FLOW CONTROL: None

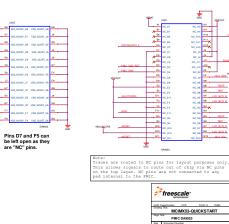

#### 3.15. JTAG Connector (J15)

A standard 20-pin ARM JTAG connector is provided on the Quick Start board. Logic signals to the JTAG connector are 1.8V signals. A 1.8V reference signal is provided to pin 1 of the connector so that the attached JTAG tool can automatically configure the logic signals for the right voltage. If the JTAG tool does not have an automatic logic voltage sense, make sure that the tool is configured for 1.8V logic.

JTAG tools that have been specifically tested with the Quick Start board are:

- JTAG Commander (Macraigor)

- DS-5 and RealView (ARM Ltd.)

- Trace32 (Lauterbach)

- J-Link (Segger/Codesourcery)

- J-Link (IAR)

#### 3.16. Expansion Header (J13)

A 120-pin Expansion Port Header is provided on the Quick Start board for use with many optionally expansion boards available from Freescale, or for custom designed boards made be the developer. At the time of initial production, the following expansion boards are available from Freescale:

- MCIMXHDMICARD HDMI signal output daughter card

- MCIMX28LCD 4.3" WVGA Touch Panel LCD Display

The Expansion Port makes the following features of the i.MX53 Processor available to be used on a custom built expansion card:

CSPI, eCSDPI2

UART4, UART5

12C1, 12C2

USBH2

AUDMUX4, AUDMUX5

- Two Serial Peripheral Interfaces (SPI)

- Two I2S/SSI/AC97 Ports

- Two Inter-Integrated Circuits (I2C)

- 2 UARTs

- SPDIF Audio

- USB ULPI Port

- 24-bit Data and display control signals

- Resistive Touch Screen Interface

- Various Voltage rails

#### 3.17. User Interface Buttons

There are four user interface buttons on the Quick Start board. Their functionality is as follows:

POWER: In the 'Power Off' state, momentarily pressing the POWER button will begin the PMIC power on cycle. The PMIC supplied voltage rails will come up in the proper sequence to power the i.MX53 Processor. When the processor is fully powered, the boot cycle will be initiated.

In the 'Power On' state, momentarily pressing the POWER button will send a signal to a GPIO port for user defined action, but will not initiate a hardware shutdown.

In the 'Power On' state, holding the power button down for greater than 5 seconds will result in the PMIC initiating a shutdown to the 'Standby' power condition. This will also be the result from the 'Power Off' state as the PMIC will transition into the 'Power On' state and will still see the POWER button as held down.

#### Hardware Reference Manual for i.MX53 Quick Start

RESET: Pressing the RESET button in the 'Power On' state will force the i.MX53 Applications Processor to immediately turn off, and reinitiate a boot cycle from the Processor Power Off state. The RESET button has no effect on the PMIC or the voltage rails.

Pressing the RESET button when the Quick Start board is powered off will have no effect.

USERDEF1: These two buttons are user defined buttons attached to PATA\_DATA14 (P6) for

USERDEF2: USERDEF1 and PATA\_DATA15 (P5) for USERDEF2. The two GPIO pins are normally pulled high by an internal resistor. The two buttons function by connecting the pins to ground, thus inserting a low signal. The developer is left to determine the actions of these two pins in code. Sample codes do not assign functionality to either pin.

#### **3.18. User Interface LED Indicators**

There are eight LED status indicators located next to the microSD card connector. These LEDs have the following functions:

| 5V:   | <ul> <li>The 5V status LED (D1) is a Green LED connected directly to the 5V_MAIN power rail.</li> <li>This LED indicates that 5V wall power is being properly supplied to the Quick Start board. If this light is not lit, it would indicate one of three problems: <ol> <li>Fuse F1 has been blown and needs to be replaced.</li> <li>Voltage from the wall supply is greater than 5.5V and the over voltage protection feature is disabling power to the board.</li> <li>The DC Power supply is not plugged in or malfunctioning.</li> </ol> </li> </ul> |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PMIC: | The PMIC status LED (D9) is a Green LED gated by the PMIC SYS_UP signal from the PMIC. This LED indicates that the PMIC is in the fully on condition and supplying power to the processor and other voltage rails as directed by software.                                                                                                                                                                                                                                                                                                                 |  |

| USER: | The User status LED (D16) is a Green LED gated by the PATA_DATA1 (L3) GPIO pin. The developer is left to determine the action of this pin in code. Sample codes do not assign functionality to the pin. The LED comes on by default when the processor starts up.                                                                                                                                                                                                                                                                                          |  |

| FLT:  | The FLT status LED (D14) is a Red LED gated by the NVDD_FAULT signal from the PMIC.<br>The LED will turn on anytime the PMIC is not outputting the requested voltages or when<br>the PMIC senses a fault condition and will begin to power down the voltage rails. This<br>may aid in trouble shooting power problems if both the PMIC and FLT LEDs are on at the<br>same time, it indicates that the PMIC is causing a shutdown based on a fault it has<br>sensed.                                                                                        |  |

| 3.3V: | The 3.3V status LED (D10) is a Blue LED gated by the External Regulator 3.2V power rail.<br>This power rail can be turned off by software for power savings measures. This LED provides an easy visual recognition as to the status of this bus.                                                                                                                                                                                                                                                                                                           |  |

SATA: The SATA status LED (D11) is a Blue LED gated by the SATA\_1V3 (VLDO5) power rail. This power rail can be turned off by software for power savings measures. This LED provides an easy visual recognition as to the status of this bus.

VGA: The VGA status LED (D12) is a Blue LED gated by the TVDAC\_2V75 (VLDO7) power rail. This power rail can be turned off by software for power savings measures. This LED provides an easy visual recognition as to the status of this bus.

LCD: The LCD status LED (D13) is a Blue LED gated by the LCD\_3V2 power rail. Normally the LCD\_3V2 power rail receives power directly from the DCDC\_3V2 power rail, but the LCD can also be configured to receive power from VIOHI\_2V772 (VLDO4). In the alternate voltage supply configuration, this LED will provide visual recognition as to the status of the LCD will provide visual recognition as to the status of the LCD bus.

### 3.19. Optional Li-ION Battery Connector (J14)

On the Quick Start board, there is a footprint (J14) available to solder a three pin wafer connector (Molex 0530470310 or equivalent). This connector will mate to Li-ION batteries commercially available as replacement batteries to commonly available MP3 players. The developer should make sure that the polarity of the battery matches the polarity of the connector as replacement batteries may vary from different manufacturers. When installed, a battery can be charged from the external 5V wall power source. A battery will not be charged when only a USB cable is connected to the Quick Start board. When powering a board from only a battery, the 5V power rail and the DCDC\_3V2 power rail will not be powered. Therefore, the Ethernet subsystem and Audio subsystem will not be operational under normal board configurations. Depending on the battery capacity, it may be necessary to power down additional subsystem voltage rails to extend battery life to a usable amount.

The battery charging feature is an autonomous operation of the Dialog DA9053 PMIC that does not require software support. Battery charging may be prevented by software by making registry changes to the PMIC. The developer may need to verify in software that PMIC registry settings are proper for battery charging operations. The footprints for testing with a battery were included for skilled developers looking to experiment.

### 3.20. Optional Back-Up Coin Cell posts (JP1, JP2)

On the Quick Start board, there are two through-holes (JP1 and JP2) next to the power connector. These through-holes are positioned to hold a Lithium coin cell battery (Sanyo ML1220-VM1 or equivalent). For proper operation, the coin cell posts should be soldered direction to the Quick Start board, with the positive terminal connected to JP1 and the negative terminal connected to JP2. The DA9053 PMIC will charge the coin cell when 5V Wall Power is available. When 5V Wall Power is removed, the coin cell will provide power only to the RTC power rail (VLDO1) supplying power to the i.MX53 processor. The length of time a coin cell can power the RTC subsystem may vary.

#### **3.21. PCB Shorting Traces**

On the Quick Start PCB, there are 29 sets of standard footprints with a copper trace between them to short the two pads together. The PCB is produced with these pads unpopulated. These shorting traces are placed throughout the PCB at locations in line with major power rails and critical components. The purpose of these shorting traces it to allow the skilled developer to manually cut the trace between the pads to either:

- 1) Isolate power to major subsystems or components.

- 2) Install small value precision resistors to measure current consumption of major subsystems.

- 3) Or reconfigure power sources to subsystems or components using wires soldered to the pads.

To restore a shorting trace back to normal after the trace is cut, it is only necessary to solder a Zero Ohm resistor to the pads.

#### 4. Quick Start Board Connectors and Expansion Port

The Quick Start board provides a number of connectors for a variety of inputs and outputs to and from the board. The following subsections describe these connections in detail.

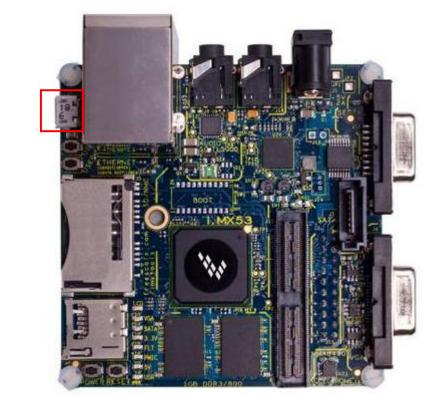

#### 4.1.Wall 5V Power Jack (J1)

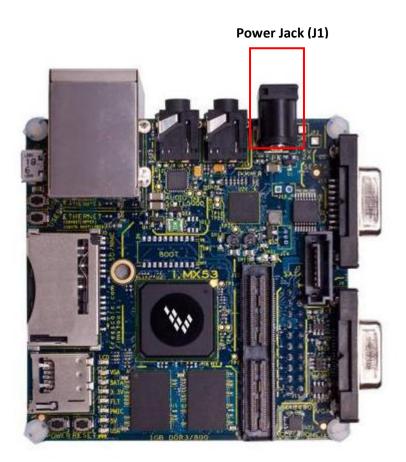

The 5V/2A AC-to-DC power supply that comes with the Quick Start board is plugged into the Power Jack (J1) on the board as show in **Figure 1**. If the original power supply is lost, it is possible to use a substitute power supply for the Quick Start board. Voltage above 5.5V, and below 12V, will trigger the Over-Voltage protection circuitry on the board. It is not recommended to use a higher voltage since, in the event of a failure to the protection circuitry, damage to the board will result. A voltage supply above 12V will damage the PMIC part.

Figure 1. DC Power Jack

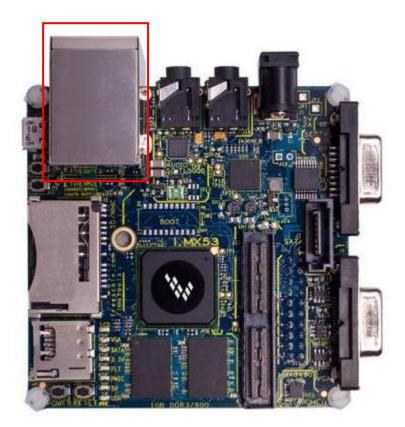

#### 4.2. RJ45 Ethernet Connector (J2B)

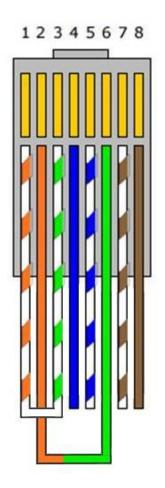

A standard Cat-V Ethernet cable is attached to the Quick Start board at the Ethernet/Dual USB connector J2. The connector contains integrated magnetic which allows the Ethernet IC to auto configure the port for the correct connection to either a switch or directly to a host PC on a peer-to-peer network. It is not necessary to use a crossover cable when connecting directly to another computer. The Ethernet/Dual USB connector is shown in **Figure 2**.

Figure 2a. Ethernet Port

Figure 2. RJ45 Ethernet Connector

#### Ethernet/Dual USB Connector (J2)

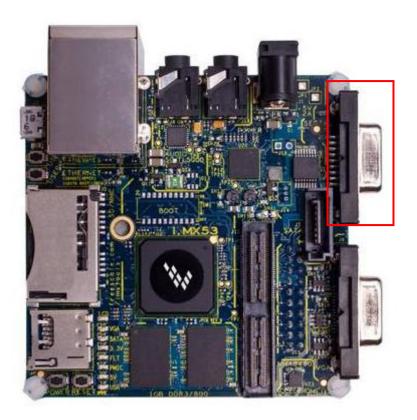

### 4.3. VGA DB15 Connector (J8)

To connect the Quick Start board to a computer monitor in the base configuration, a VGA cable is required. Connect the free end of the VGA cable to connector J8 to the point shown in **Figure 3**.

VGA DB15 Connector (J8)

Figure 3. VGA Connector

#### 4.4. Debug UART DB9 Connector (J16)

To connect a host PC to the Quick Start board to receive Debugging information, a Null Modem serial cable is required. This cable is not supplied with the Quick Start kit. The male plug end of the serial cable is connected to the board at the point shown in **Figure 4**. The other end of the serial cable is connected to a PC. For newer generation computers that do not have a serial port, a USB-to-Serial cable can be used. There is no need for any special cabling to support debug information output.

Debug UART DB9 Connector (J16)

Figure 4. Debug UART Connector

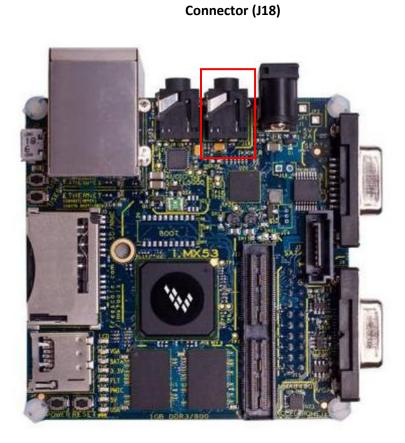

#### 4.5. Headphone Output Connector (J18)

Any set of ear buds or head phones with a standard 3.5mm stereo jack can be connected to the Audio Output jack at the point shown in **Figure 5.** Ear buds are not supplied as part of the Quick Start kit.

Head Phone

Figure 5. Headphone Output Connector

#### 4.6. Microphone Input Connector (J6)

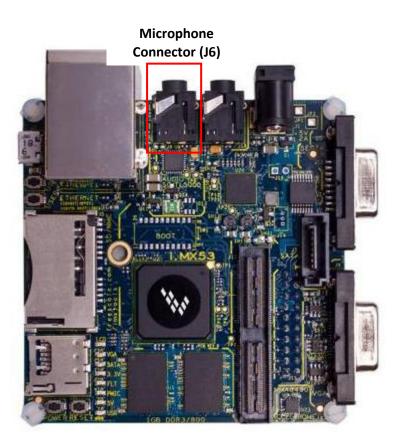

The Quick Start board provides a 3.5mm stereo connector for a microphone input. The microphone is not provided as part of the Quick Start kit. The developer has several choices as to the type of device plugged into this connector. A mono microphone will input its signal though the tip of the 3.5mm plug. The microphone bias is applied on the Quick Start board, therefore a microphone which uses a wire to send the bias signal to the actual condenser is not necessary, but will not interfere with the microphone operation. The Quick Start board can also be configured for use with a microphone/mono-output ear bud commonly used on cellular phones. To have right channel sound output on this connector, it would be necessary for the developer to move the ferrite bead from the L25 pads and solder it to the L22 pads. This will remove the signal from the headphone output connector. The developer may also find it necessary to use a 2.5mm to 3.5mm adapter with most cellular microphone/earphone sets. As manufactured, the developer may also use a two plug headphone, microphone set commonly used for VOIP services on a PC. The microphone is connecter at the point shown in **Figure 6**.

Figure 6. Microphone Connector (J6)

### 4.7. Dual USB Host Jack (J2)

The Quick Start board has two USB Host only connectors that can be used to support USB devices. The upper USB port is connected to the High-speed (HS) USB 2.0 module of the i.MX53 processor and can support; 1) Any single, high-power USB device, 2) Any combination of USB devices though a self-powered hub not to exceed 500 mA current draw, or 3) Any combination of USB devices through a powered hub. The lower USB port is connected to the High-speed (HS) USB 2.0 OTG module of the i.MX53 processor and is cross-connected with the micro-B USB device connector (J3). As long as the Quick Start board is not connected to a USB Host device through the micro-B USB connector, the same combinations of USB devices can be used on the lower port as used on the upper port. The lower USB port requires configuration as a Host port in software, and is not available as a Host port during the initial boot sequence. USB cables can be inserted into the Dual USB connector at the point shown in **Figure 7**.

Figure 7a. USB Connectors

Figure 7. Dual USB Host Connectors (J2)

#### 4.8. micro-B USB Device Connector (J3)

The Quick Start board has one micro-B USB device connector that can be used to connect the Quick Start board to a USB Host computer. The micro-B connector is connected to the High-speed (HS) USB 2.0 OTG module of the i.MX53 processor and is cross connected with the lower USB Host port on J2. When a 5V supply is seen on the micro-B connector (from the USB Host), the i.MX53 processor will configure the OTG module for device mode, which will prevent the lower USB Host port from operating correctly. The 5V power provided by the attached USB Host is only used by the i.MX53 processor for sensing that the host is present. The Quick Start board will not draw power from the connected USB Host and will not operate without a 5V DC power source or charged Li-ION battery. The micro-B connector is keyed and will not accept a micro-A plug from a cable. A micro-B to USB-A cable is supplied as part of the Quick Start kit and can be inserted into the micro-B USB connector at the point shown in **Figure 8**.

micro-B USB Connector (J3)

Figure 8. micro-B USB Device Connector (J3)

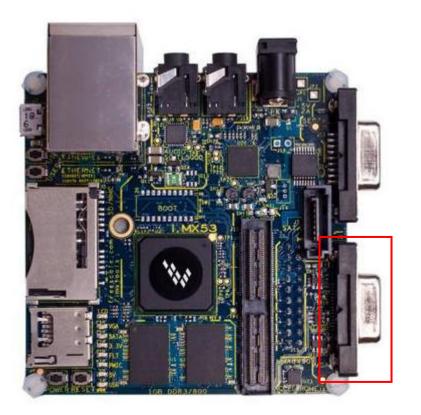

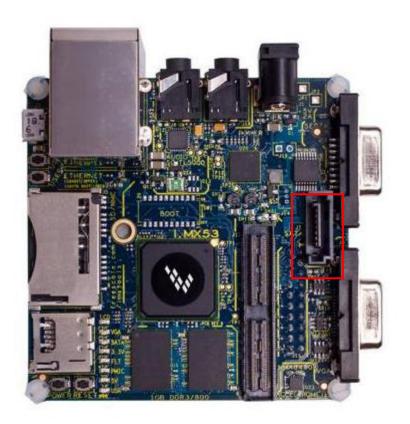

#### 4.9. SATA 7-pin Data Connector (J7)

A SATA 7-pin Data connector (J7) is provided on the Quick Start Board and is connected to the SATA module of the i.MX53 processor. The Quick Start board is capable of communicating with any standard SATA device, such as a hard drive or optical DVD/CD reader. The SATA device, SATA cables and power supply for the SATA device are not provides as part of the Quick Start kit and are the responsibility of the developer. It is possible to initiate a boot from an attached SATA device. See the software reference manuals for instructions on how to configure the Quick Start board for SATA boot. The SATA Data cable is plugged into the Quick Start board at the location shown in **Figure 9**.

SATA 7-pin Data Connector (J7)

Figure 9. SATA Data Connector (J7)

#### 4.10. SD Card Connector (J5)

The Quick Start board has one full size SD/MMC connector that can be used for memory, or for thirdparty SDIO type cards such as WiFi or Bluetooth. The SD Card Connector (J5) connects a full 8-bit parallel data bus to the SD3 port of the i.MX53 processor. The SD Card Connector receives power from the DCDC\_3V2 power rail supplied by the supplementary Voltage Regulator. The Quick Start board does not come pre-configured to boot from the full size SD Card Connector, but the board can be modified to support booting from this connector instead of the microSD Card Connector. See the section on Quick Start boot options on how to make the necessary changes (Section 5.4.2). The SD Card Connector is not spring loaded, so pushing the card into the slot will not initiate an action to disengage the SD Card. The SD Card is inserted facing up at the location shown in **Figure 10**.

SD Card Connector (J5)

Figure 10. SD Card Connector (J5)

### 4.11. microSD Card Connector (J4)

The Quick Start board has one micro SD/MMC connector that can be used for memory. The micro SD Card Connector (J4) connects a 4-bit parallel data bus to the SD1 port of the i.MX53 processor. The micro SD Card Connector receives power from the VLDO3 power rail. The Quick Start board comes configured to boot from the micro SD Card Connector by default. The micro SD Card Connector is spring loaded and will eject a properly inserted card if the card is pushed in again. Caution: If the card is ejected while serving as the file system, the processor will undergo a software crash. The micro SD Card is inserted facing up at the location shown in **Figure 11**.

microSD Connector (J4)

Figure 11. microSD Card Connector (J4)

JTAG Connector (J15)

#### 4.12. 20-pin ARM JTAG Connector (J15)

The Quick Start board contains a standard 20-pin ARM JTAG connector (J15) for advanced debugging with a third-party emulator. The header is configured for use with 1.8V data signals. The developer should exercise caution when selecting the appropriate debugging tools. If an emulator set for 3.3V power and data is connected to the Quick Start board, the i.MX53 processor will be damaged. The emulator JTAG cable is connected to the bottom side of the Quick Start board at the location shown in **Figure 12**.

Figure 12. JTAG Connector (J15)

#### 4.13. LVDS Connector (J9)

The Quick Start board includes a 30-pin (Hirose, DF19G-30P-1H(56)) connector for use with an LVDS display. The developer can create custom cables that will allow the Quick Start board to be used with a wide variety of commercially available LVDS displays. The pin-out for this connector is used on other Freescale designed boards in the i.MX53 series, such as the MCIMX53SMD tablet. Freescale has available a cable and LVDS display (HannStar, HSD100PXN1-A00-C11) for purchase if the developer wishes to use a pre-tested configuration. The LVDS display can be used in conjunction with the optional LCD display, the VGA output or the optional HDMI card, as long as the total video output does not exceed the specified limits of the i.MX53 processor. The pin-out table for the connector is located in different section of this user guide. This connector is located on the bottom side of the board in the location shown in **Figure 13**.

LDVS Connector (J9)

Figure 13. LDVS Connector (J9)

# 5. Quick Start Board Architecture and Design

This section is designed to provide the developer detailed information about the electrical design and practical considerations that went into the Quick Start board. This section is organized to discuss each block in the following high level block diagram of the Quick Start board, as shown in **Figure 14**.

Figure 14. i.MX53 Smart-Start Block Diagram

### 5.1. 5V Power Supply

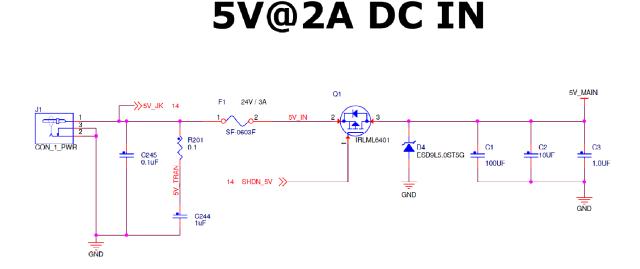

5V power from an external wall power supply is connected to the Quick Start board at connector J1. From the connector, the 5V supply is sent directly to a 3A over current protection fuse (F1). In between the connector and the fuse, there are two capacitors to bleed off voltage transients and a single trace that leads to the sense pin for the over-voltage protection circuitry of the Dialog PMIC. From the protection fuse, the 5V supply is connected to the over-voltage protection POWERFET Q1 which is controlled by the PMIC. This circuit limits to a very small area of the Quick Start board the physical location of where unprotected 5V power can reach. The 5V\_MAIN power seen by the rest of the Quick Start board is protected from over-voltage and over-current. The circuit is shown below in **Figure 15**.

#### Figure 15. Board Main Power Circuit.

# 5.2. Dialog DA9053 PMIC

The Dialog PMIC provides all regulated power to the Quick Start board with the exception of a supplemental 3.2V/1A voltage regulator. Physically, the PMIC is located in the upper right corner of the Quick Start board, as close to the power connector as possible, while still maintaining room for supporting components. From this location, power is supplied to the rest of the board.

When 5V power is first attached to the Quick Start board, the PMIC will remain in an OFF state until the POWER button is pressed. In the OFF state, the PMIC will generate power on the VDDOUT rail at approximately 3.6V (different if Li-ION battery attached) for use by the PMIC as a supply for all regulators. In addition, the PMIC generates a VDDCORE voltage of 2.5V for internal PMIC use, and to serve as a pull-up source for the nONKEY/KEEPACT and nSHUTDOWN control inputs. This ensures that these two button are active whenever power is available to the Quick Start boar.

When the POWER button is initially pressed, the PMIC senses the Active Low signal on the nONKEY pin and begins to power on all voltage rails in preprogrammed sequence. The sequence is determined primarily by the order in which power must be supplied to the i.MX53 processor. Once the core operations of the processor are fully powered, other power rails are turned on.

The first voltage regulator to power on is always VLDO1. This regulator supplies a maximum of 40 mA current at 1.3V and powers on only the Secure RTC module of the i.MX53 Processor. This turns on the RTC Clock (32.768KHz) and Watch Dog features. In the event a System Reset is triggered, or the Quick Start board is placed into Standby, VLDO1 will remain powered ON. The only time that VLDO1 will turn off is if all power is removed from the Quick Start board, or if a software command is sent to the PMIC to turn off VLDO1. In the case that a developer attaches an optional coin cell to JP1/JP2, the coin cell will provide power to keep VLDO1 operating.

The power sequence requirements for the i.MX53 Applications Processor from the data sheet are as follows:

- 1. NVCC\_SRTC\_POW (VLDO1)

- 2. VCC, VDDA, VDDGP, VDD\_REG [in any order]

- 3. All other supplies [in any order]

NOTE: in case the internal regulator is used for VDDA generation, the VDD\_REG should be powered up together with VCC and VDDGP, before the other supplies. In case the internal regulator is not used to generate VDDA (as on the Quick Start board), the VDD\_REG is independent and has no power-up restrictions.

The power on timing sequence shown in **Table 1** is the sequence programmed into the Dialog PMIC. It is one way of providing sequences power to the i.MX53 processor. Designers are free to change the power timing sequence on their own board designs as long as the timing requirements are met. Freescale has not formally tested other power on timing sequences.

| Regulator    | Time Slot |

|--------------|-----------|

| VBUCKPRO     | 19 mSEC   |

| VBUCKPERI    | 23 mSEC   |

| VLDO6        |           |

| VLDO8        |           |

| VLDO10       |           |

| VBUCKCORE    | 27 mSEC   |

| VBUCKMEM     | 31 mSEC   |

| VBUCKPERI/SW |           |

| VLDO2        |           |

| VLDO5        |           |

| VLDO4        | 35 mSEC   |

| VLDO7        |           |

| VLDO3        | 64 mSEC   |

| VLDO9        |           |

| DCDC_3V2     |           |

#### Table 1. Regulator Timing Sequence

The Dialog PMIC will enter a SHUTDOWN/STANDBY condition by one of three ways; By a command from the i.MX53 Processor via I2C communications, by i.MX53 Processor action to hold the nONKEY/KEEPACT pin low for at least five seconds, or by hardware if the user holds down the POWER button for more than five seconds. All three actions result in the Dialog PMIC powering down the voltage regulators in reverse order of the power on sequence, except for VLDO1. A subsequent press of the POWER button will initiate the same power on sequence as shown in **Table 1**.

The various power rails supplied by the PMIC are discussed in the section on Quick Start Power Rails. Other features of the Dialog PMIC implemented by the Quick Start board are discussed in subsequent sub-sections including: Li-ION Battery Charging, Backlight LED Driver, Touch-Screen Operation, Miscellaneous.

### 5.2.1. Quick Start Power Rails

**Table 2** shows all the voltage supply rails used on the Quick Start board, their voltages and the major subsystems they supply on the board:

| Regulator    | Voltage        | Named Rails        | Powers             |

|--------------|----------------|--------------------|--------------------|

| VBUCKCORE    | 1.1V           | VBUCKCORE VDDGP    | VDDGP              |

| VBUCKPRO     | 1.3V           | VBUCKPRO VCC_1V3   | VCC                |

| VBUCKMEM     | 1.5V           | VBUCKMEM DDR_1.5V  | NVCC_EMI_DRAM      |

|              |                | DDRQ_1.5V          | DDR3 SDRAM         |

| VBUCKMEM/SW  | 1.5V           | VMEM_SW            | ALTERNATE FOR:     |

|              |                | DDR_1.5V (ALT)     | DDR3 SDRAM LOGIC   |

|              |                | DDRQ_1.5V (ALT)    | DDR3 SDRAM CORE    |

| VBUCKPERI    | 2.5V           | VBUCKPERI          | VDD_REG            |

|              |                | VDD_REG_2V5        | NVCC_XTAL          |

|              |                | NVCC_XTAL_2V5      | ALTERNATE FOR:     |

|              |                | LVDS_2V5 (ALT)     | LVDS MODULE        |

|              |                | SATA_PHY_2V5 (ALT) | SATA MODULE        |

|              |                | VUSB_2V5 (ALT)     | USB MODULE 2.5V    |

| VBUCKPERI/SW | 2.5V           | VPERI_SW           | LVDS MODULE        |

|              |                | LVDS_2V5           | SATA MODULE        |

|              |                | SATA_PHY_2V5       | USB MODULE 2.5V    |

|              |                | VUSB_2V5           |                    |

| BOOST        | Current Source | VLCD_BLT           | EXPANSION PORT LCD |

|              |                |                    | BACKLIGHT SUPPLY   |

| VLDO1        | 1.3V           | VLDO1_1V3_RTC      | NVCC_SRTC          |

|              |                | NVCC_SRTC          |                    |

| VLDO2        | 1.3V           | DIG_PLL_1V3        | ALTERNATE FOR:     |

|              |                |                    | DIG_PLL            |

| VLDO3        | 3.3V           | VLDO3_3V3 SD1_3V3  | MICROSD CARD (SD1) |

|              |                |                    | 12C1/12C2          |

|              |                |                    | BOOT_SEL           |

|              |                |                    | NVCC-EIM-MAIN      |

|              |                |                    | NVCC_EIM_SEC       |

|              |                |                    | NVCC_SD1&2         |

|              |                |                    | NVCC_PATA          |

|              |                |                    | NVCC_FEC           |

|              |                |                    | NVCC_GPIO          |

|              |                |                    | NVCC_KEYPAD        |

#### Table 2.Quick Start Board Power Supply Rails

| <b>F</b> |        |                     | Т                    |

|----------|--------|---------------------|----------------------|

| VLDO4    | 2.775V | VIOHI_2V775 LCD_3V2 | NVCC_LCD1            |

|          |        | (ALT)               | NVCC_LCD2            |

|          |        |                     | EXPANSION PORT (LCD) |

| VLDO5    | 1.3V   | VLDO5_1V3 SATA_1V3  | SATA MODULE 1.3V     |

| VLDO6    | 1.3V   | VLDO6_1V3           | VDDAL                |

|          |        | VDDAL_1V3           |                      |

| VLDO7    | 2.75V  | VLDO7_2V75          | VGA MODULE (TV DCA)  |

|          |        | TVDAC_2V75          |                      |

| VLDO8    | 1.8V   | VLDO8_1V8           | NVCC_RESET           |

|          |        |                     | NVCC_JTAG            |

|          |        |                     | NVCC_CKIH            |

|          |        |                     | NVCC_NANDF           |

|          |        |                     | NVCC_CSI             |

|          |        |                     | VDD_ANA_PLL          |

|          |        |                     | BOOT_SEL             |

| VLDO9    | 1.5V   | VLDO9_1V5           | EXPANSION PORT       |

| VLDO10   | 1.3V   | VLDO10_1V3          | VDDAL                |

|          |        | VDDA_1V3            |                      |

| DCDC-3V2 | 3.2V   | DCDC-3V2            | ETHERNET             |

|          |        | AUDIO_3V2           | AUDIO                |

|          |        | FEC_3V2             | VGA_IO_SIGNALS       |

|          |        | VDD_FUSE            | USB 3.3V             |

|          |        | LCD_3V2             | SD CARD (SD3)        |

|          |        |                     | EXPANSION PORT       |

### Table 2. Quick Start Board Power Supply Rails (con)

### 5.2.2. Li-ION Battery Charging

The Dialog PMIC contains a fully autonomous Li-ION battery charger. When wall power is first applied to the Quick Start board, the PMIC will begin to apply a pre-charge to the positive battery terminal. If the PMIC senses a fully discharged battery or a fault condition (eg, no battery), the PMIC will disconnect VDDOUT from the battery and allow the regulators to receive power independent what is attached to VBAT. The footprints for testing with a battery were included for skilled developers looking to experiment. As manufactured, the Quick Start board does not support Li\_ION battery operations without modifications by the developer.

If the PMIC senses the battery voltage above the BAT\_FAULT threshold for 40 msec, the PMIC will then begin a fast linear charge of the Li-ION battery by controlling the voltage on VDDOUT. If the PMIC is unable to increase VDDOUT above VBAT to continue charging the battery, the PMIC has an alternate current charging method using an active diode. Charging will continue until the battery voltage reaches the programmed level. The Li-ION charging circuit also makes use of a temperature sensor (thermistor) attached to the body of the battery. If the resulting voltage measurement at TBAT falls outside the threshold value programmed into the registry settings, the PMIC will suspend the charging current until the battery temperature reduces back to with the threshold values. See the Dialog PMIC datasheet for a more detailed explanation.

The PMIC is initially programmed with default settings to charge most Li-ION batteries. These settings may be changed by software and the software documentation should be consulted for actually PMIC registry values. These values can be changed in software as the developer sees fit. For more detailed information on how the battery charging function works and how to change default charging parameters. Since the 5V power pin of the USB micro-B connector is not connected to the PMIC, all discussion concerning battery charge current limits due to exceeding the USB standards do not apply to the Quick Start board.

In designing a board using the Dialog PMIC, it is important to include a capacitor of 47 uF or greater attached to the VBAT pin if any operations are planned without a Li-ION battery. If during the initial pre-charge phase, the Dialog PMIC does not sense any voltage present when the pre-charge voltage is momentarily removed and VBAT voltage is measured, the PMIC will assume a massive board failure and will not supply any voltage via the regulators.

#### 5.2.3. Backlight LED Driver

The Dialog PMIC provides a Boost circuit which controls an external MOSFET Q8. The PMIC is capable of driving 3 independent strings of up to 5 white LEDs each with a voltage of approximately 24 Volts and a maximum of 50 mA. The Quick Start board does not have a direct connection for white backlight LEDs, but does supply one connection to the Expansion Port that can be used to support an attached LCD Daughter Card. The Expansion Port uses the LED1\_IN port of the PMIC.

When designing a circuit to use the Backlight LED driver, it is important to connect the cathode (negative) end of the LED string directly to the LED\_IN port of the PMIC. The PMIC controls the supply voltage to the Backlight LEDs by ensuring that the voltage sensed on the LED\_IN port is above a threshold voltage of 0.7V. If more than one LED\_IN ports are used, the lowest port must be above the threshold value. If the designer connects the cathode end of the Backlight LED string to GROUND, the boost circuit will not work.

The MOSFET used in the boost circuit should have a low ON Resistance value for best efficiency. The MOSTFET chosen for the Quick Start board, ON Semiconductor NTLJF4156NT1G, also contains a necessary diode used in the boost circuitry. This helps reduce the number of components.

### 5.2.4. Touch-Screen Operation

The Dialog PMIC contains an autonomous Touch Screen Interface which will measure the XY positions from a standard 4-WIRE resistive touch panel. The single ADC channel will detect the presence of a pen touch on the panel, and that will trigger a series of voltage measurements on each of the four touch panel wires (X+, X-, Y+, Y-) by the ADC in a pre-selected sequence. The resulting voltage readings are then reported to the i.MX53 Applications Processor for conversion to a panel X-Y position via the I2C communications link.

To ensure the Touch Screen Interface wakes up autonomously with a pen stroke, it is necessary to supply a 1.8V reference voltage to the TSIREF\_GPIO\_7 pin of the PMIC. It is recommended that one of the high PSSR Regulators of the PMIC be used to supply this voltage. VLDO6 – VLDO9 are possible sources for supplying this reference voltage.

### 5.2.5. Miscellaneous

If a coin cell battery is attached to the Quick Start board, it will automatically charge using the programmed charging settings whenever wall power is supplied to the Quick Start board. When the battery voltage reaches the programmed level, charging will stop. Battery discharge will not begin until wall power is removed from the board and, if a Li-ION battery is attached, the main battery discharges to the battery cut off level.